## 10 输出低抖动低功率时钟缓冲器和电平转换器

查询样片: **CDCLVC1310**

### 特性

- 支持 **-169dBc/Hz** 超低本底噪声的高性能晶振缓冲器

- 附加的相位噪声/抖动性能为 **25 fs<sub>RMS</sub>** (典型值)

- 具有 **3.3V** 或 **2.5V** 内核电压和 **3.3V, 2.5V, 1.8V** 或 **1.5V** 输出电源的电平转换

- 器件输入包括主级、次级和晶振输入并可使用输入 **MUX** 进行手工选择 (通过引脚)。主级和次级输入能够接受低电压正射极耦合逻辑 (**LVPECL**)，低压差分信号 (**LVDS**)，主机时钟信号电平 (**HCSL**)，**SSTL** 或者低压 **CMOS (LVCMOS)** 信号和晶振输入。

- 支持 **8MHz** 至 **50MHz** 的晶振频率

- 支持高达 **200MHz** 的差分和单端输入频率。

- 10** 个单端 **LVCMOS** 输出。输入可运行在 **1.5V, 1.8V, 2.5V** 或者 **3.3V** 的电源电压下。

- LVCOMS** 输出运行频率高达 **200MHz**

- 输出偏移为 **30ps** (典型值)

- 总传播延迟为 **2ns** (典型值)

- 同步和无毛刺脉冲输出启用可用

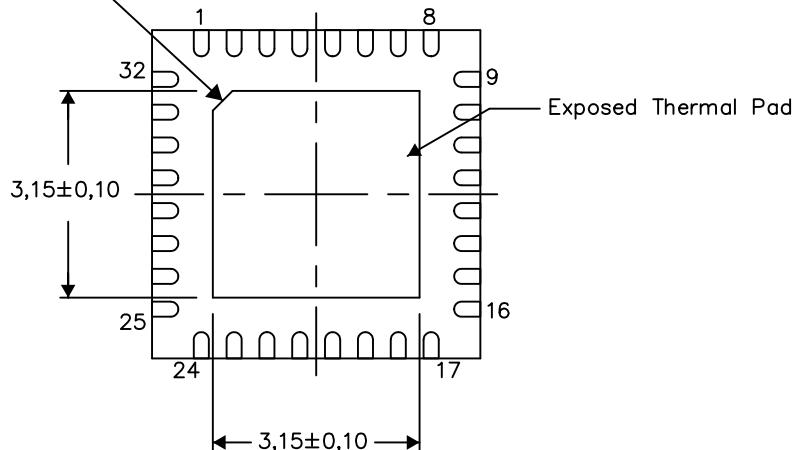

- 采用方形扁平无引脚 (**QFN)-32 5mm x 5mm** 封装，其工业温度范围为**-40°C** 至 **85°C**。

- 能够过度驱动 **LVCOMS** 信号高达 **50MHz** 的晶振输入

### 应用范围

- 无线和有线基础设施

- 网络和数据通信

- 医疗成像

- 便携式测试和测量

- 高端 **A/V**

### 说明

CDCLVC1310 是一款多用途、低抖动、低功率时钟扇出缓冲器，此缓冲器可将来自 3 个输入中的 1 个分配到 10 个低抖动 **LVCOMS** 时钟输出，这 3 个输入的主和副输入特有差分或者单端信号和晶振输入。此类缓冲器适合用于多种移动和有线基础设施、数据通信、计算、低功率医疗成像和便携式测试和测量应用。当输入为非法电平时，此输出在一个确定的状态上。可将内核电压设定在 **2.5V** 或 **3.3V** 上，将输出设定在 **1.5V, 1.8V, 2.5V** 或 **3.3V** 上。引脚编程可轻松地配置 CDCLVC1310。总体附加抖动性能为 **25fs<sub>RMS</sub>** (典型值)。CDCLVC1310 封装在小型 32 引脚 **5mm x 5mm QFN** 封装内。

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

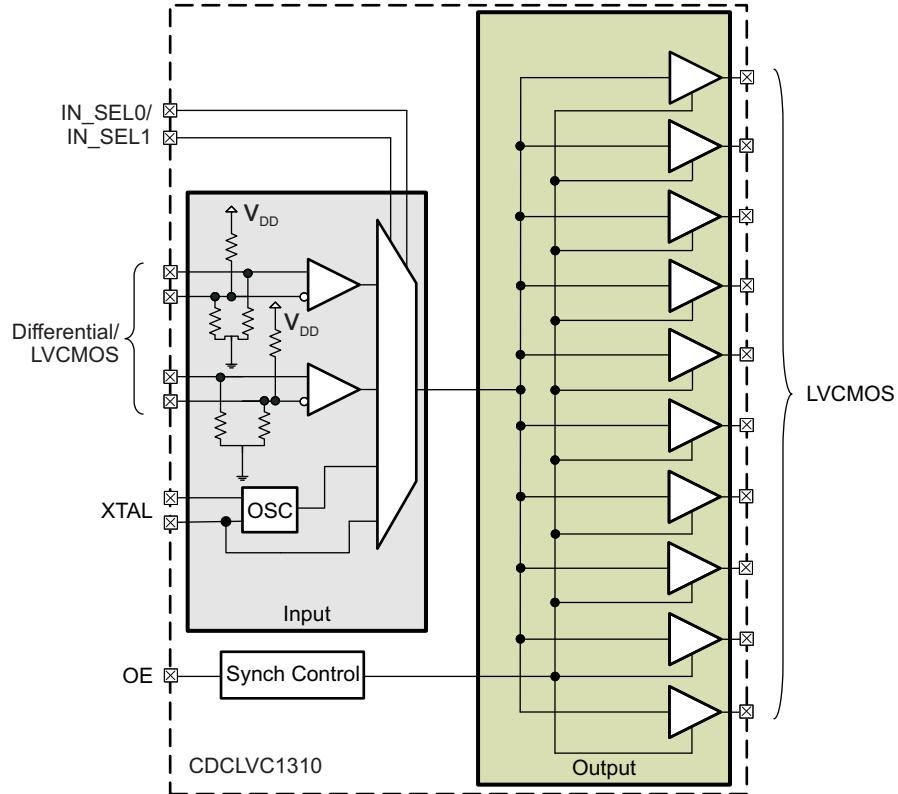

## BLOCK DIAGRAM

Figure 1. High-Level Block Diagram of CDCLVC1310

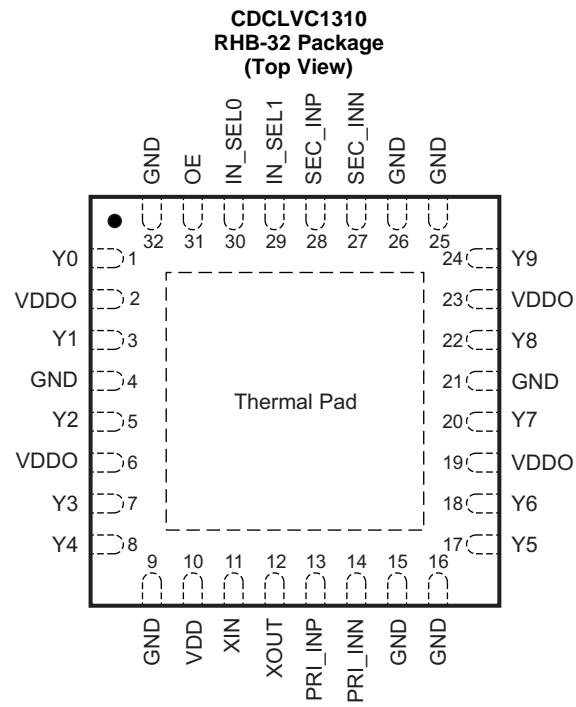

## PINOUT DIAGRAM

P0048-18

## PIN FUNCTIONS

| PIN                 |                                       | I/O | TYPE    | DESCRIPTION                                                                                                   |

|---------------------|---------------------------------------|-----|---------|---------------------------------------------------------------------------------------------------------------|

| NAME                | NO(s)                                 |     |         |                                                                                                               |

| GND                 | 4, 9, 15,<br>16, 21,<br>25, 26,<br>32 | PWR | Analog  | Power-supply ground                                                                                           |

| IN_SEL0,<br>IN_SEL1 | 30, 29                                | I   | Digital | Input-clock selection (pulldown of 150 kΩ)                                                                    |

| OE                  | 31                                    | I   | Digital | LVCMS output enable (pulldown of 150 kΩ)                                                                      |

| PRI_INN             | 14                                    | I   | Analog  | Inverting differential primary reference input, internally biased to Vdd / 2 (pullup or pulldown of 150 kΩ)   |

| PRI_INP             | 13                                    | I   | Analog  | Non-inverting differential or single-ended primary reference input (pulldown of 150 kΩ)                       |

| SEC_INN             | 27                                    | I   | Analog  | Inverting differential secondary reference input, internally biased to Vdd / 2 (pullup or pulldown of 150 kΩ) |

| SEC_INP             | 28                                    | I   | Analog  | Non-inverting differential or single-ended secondary reference input (pulldown of 150 kΩ)                     |

| VDD                 | 10                                    | PWR | Analog  | Power-supply pins                                                                                             |

| VDDO                | 2, 6, 19,<br>23                       | PWR | Analog  | I/O power-supply pins                                                                                         |

| XIN                 | 11                                    | I   | Analog  | Crystal-oscillator input or XTAL bypass mode                                                                  |

| XOUT                | 12                                    | I   | Analog  | Crystal-oscillator output                                                                                     |

| Y0                  | 1                                     | O   | Analog  | LVCMS output 0                                                                                                |

| Y1                  | 3                                     | O   | Analog  | LVCMS output 1                                                                                                |

| Y2                  | 5                                     | O   | Analog  | LVCMS output 2                                                                                                |

| Y3                  | 7                                     | O   | Analog  | LVCMS output 3                                                                                                |

| Y4                  | 8                                     | O   | Analog  | LVCMS output 4                                                                                                |

| Y5                  | 17                                    | O   | Analog  | LVCMS output 5                                                                                                |

| Y6                  | 18                                    | O   | Analog  | LVCMS output 6                                                                                                |

| Y7                  | 20                                    | O   | Analog  | LVCMS output 7                                                                                                |

| Y8                  | 22                                    | O   | Analog  | LVCMS output 8                                                                                                |

| Y9                  | 24                                    | O   | Analog  | LVCMS output 9                                                                                                |

Table 1. Input Selection

| IN_SEL1 | IN_SEL0 | INPUT CHOSEN                     |

|---------|---------|----------------------------------|

| 0       | 0       | PRI_IN                           |

| 0       | 1       | SEC_IN                           |

| 1       | 0       | XTAL or overdrive <sup>(1)</sup> |

| 1       | 1       | XTAL bypass <sup>(2)</sup>       |

(1) This mode is for XTAL input or overdrive of XTAL oscillator with LVCMS input. For characteristics; see [LVCMS OUTPUT CHARACTERISTICS](#).

(2) This mode is only XTAL bypass. For characteristics, see [LVCMS OUTPUT CHARACTERISTICS](#).

Table 2. INPUT/OUTPUT OPERATION<sup>(1)</sup>

| INPUT STATE                                        | OUTPUT STATE |

|----------------------------------------------------|--------------|

| PRI_INx, SEC_INx open                              | Logic LOW    |

| PRI_INP, SEC_INP = HIGH,<br>PRI_INN, SEC_INN = LOW | Logic HIGH   |

| PRI_INP, SEC_INP = LOW,<br>PRI_INN, SEC_INN = HIGH | Logic LOW    |

(1) Device must have switching edge to obtain output states.

**Table 3. OE Function**

| OE | Yx             |

|----|----------------|

| 0  | High-impedance |

| 1  | Enabled        |

**ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>**

over operating free-air temperature range (unless otherwise noted)

|                  |                           | VALUE              | UNIT |

|------------------|---------------------------|--------------------|------|

| VDD,<br>VDDO     | Supply-voltage range      | –0.5 to 4.6        | V    |

| V <sub>IN</sub>  | Input-voltage range       | –0.5 to VDD + 0.5  | V    |

| V <sub>OUT</sub> | Output-voltage range      | –0.5 to VDDO + 0.5 | V    |

| I <sub>IN</sub>  | Input current             | ±20                | V    |

| I <sub>OUT</sub> | Output current            | ±50                | V    |

| T <sub>stg</sub> | Storage-temperature range | –65 to 150         | °C   |

| T <sub>J</sub>   | Junction temperature      | 125                | °C   |

(1) Stresses beyond those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under *Recommended Operating Conditions* is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

**RECOMMENDED OPERATING CONDITIONS**

over operating free-air temperature range (unless otherwise noted)

|                 |                                   | MIN   | NOM | MAX   | UNIT |

|-----------------|-----------------------------------|-------|-----|-------|------|

| VDDO            | Output supply voltage             | 3.135 | 3.3 | 3.465 | V    |

|                 |                                   | 2.375 | 2.5 | 2.625 |      |

|                 |                                   | 1.6   | 1.8 | 2     |      |

|                 |                                   | 1.35  | 1.5 | 1.65  |      |

| VDD             | Core supply voltage               | 3.135 | 3.3 | 3.465 | V    |

|                 |                                   | 2.375 | 2.5 | 2.625 |      |

| I <sub>OH</sub> | High-level output current, LVCMOS |       |     | –24   | mA   |

| I <sub>OL</sub> | Low-level output current, LVCMOS  |       |     | 24    | mA   |

| T <sub>A</sub>  | Ambient temperature               | –40   |     | 85    | °C   |

## THERMAL INFORMATION

| THERMAL METRIC <sup>(1)</sup> |                                                             | CDCLVC1310 | UNIT |

|-------------------------------|-------------------------------------------------------------|------------|------|

|                               |                                                             | RHB        |      |

|                               |                                                             | 32 PINS    |      |

| $\theta_{JA}$                 | Junction-to-ambient thermal resistance <sup>(2)</sup>       | 41.7       | °C/W |

| $\theta_{JCtop}$              | Junction-to-case (top) thermal resistance <sup>(3)</sup>    | 34.1       | °C/W |

| $\theta_{JB}$                 | Junction-to-board thermal resistance <sup>(4)</sup>         | 14.4       | °C/W |

| $\psi_{JT}$                   | Junction-to-top characterization parameter <sup>(5)</sup>   | 0.9        | °C/W |

| $\psi_{JB}$                   | Junction-to-board characterization parameter <sup>(6)</sup> | 14.4       | °C/W |

| $\theta_{JCbot}$              | Junction-to-case (bottom) thermal resistance <sup>(7)</sup> | 6.2        | °C/W |

- (1) For more information about traditional and new thermal metrics, see the *IC Package Thermal Metrics* application report, [SPRA953](#).

- (2) The junction-to-ambient thermal resistance under natural convection is obtained in a simulation on a JEDEC-standard, high-K board, as specified in JESD51-7, in an environment described in JESD51-2a.

- (3) The junction-to-case (top) thermal resistance is obtained by simulating a cold plate test on the package top. No specific JEDEC-standard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

- (4) The junction-to-board thermal resistance is obtained by simulating in an environment with a ring cold plate fixture to control the PCB temperature, as described in JESD51-8.

- (5) The junction-to-top characterization parameter,  $\psi_{JT}$ , estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining  $\theta_{JA}$ , using a procedure described in JESD51-2a (sections 6 and 7).

- (6) The junction-to-board characterization parameter,  $\psi_{JB}$ , estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining  $\theta_{JA}$ , using a procedure described in JESD51-2a (sections 6 and 7).

- (7) The junction-to-case (bottom) thermal resistance is obtained by simulating a cold plate test on the exposed (power) pad. No specific JEDEC standard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

## INPUT CHARACTERISTICS

over recommended ranges of supply voltage ( $VDDO \leq VDD$ ), load and ambient temperature (unless otherwise noted)

| PARAMETER                                                              | TEST CONDITIONS                                 | MIN                               | TYP       | MAX        | UNIT |

|------------------------------------------------------------------------|-------------------------------------------------|-----------------------------------|-----------|------------|------|

| <b>DC Characteristic (OE, IN_SEL0, IN_SEL1, PRI_IN, SEC_IN)</b>        |                                                 |                                   |           |            |      |

| $I_{IH}$                                                               | Input high current                              | VDD = 3.465 V, $V_{IH} = 3.465$ V |           | 40         | μA   |

| $I_{IL}$                                                               | Input low current                               | VDD = 3.465 V, $V_{IL} = 0$ V     |           | -40        | μA   |

| $\Delta V/\Delta T$                                                    | Input edge rate                                 | 20%–80%                           |           | 2          | V/ns |

| $R_{Pullup/down}$                                                      | Pullup or pulldown resistance                   |                                   |           | 150        | kΩ   |

| $C_{IN}$                                                               | Input capacitance                               |                                   |           | 2          | pF   |

| <b>Single-Ended DC Characteristic (PRI_INP, SEC_INP)<sup>(1)</sup></b> |                                                 |                                   |           |            |      |

| $V_{IH}$                                                               | Input high voltage                              | VDD = 3.3 V ±5%                   | 2         | VDD + 0.3  | V    |

|                                                                        |                                                 | VDD = 2.5 V ±5%                   | 1.6       | VDD + 0.3  |      |

| $V_{IL}$                                                               | Input low voltage                               | VDD = 3.3 V ±5%                   | -0.3      | 1.3        | V    |

|                                                                        |                                                 | VDD = 2.5 V ±5%                   | -0.3      | 0.9        |      |

| <b>Single-Ended DC Characteristic (OE, IN_SEL0, IN_SEL1)</b>           |                                                 |                                   |           |            |      |

| $V_{IH}$                                                               | Input high voltage                              |                                   | 0.7 × VDD |            | V    |

| $V_{IL}$                                                               | Input low voltage                               |                                   |           | 0.3 × VDD  | V    |

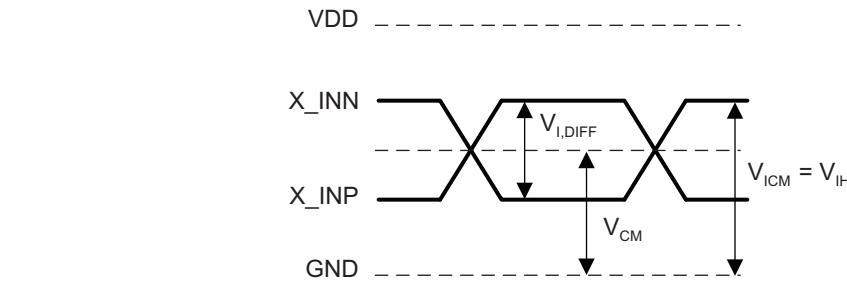

| <b>Differential DC Characteristic (PRI_IN, SEC_IN)</b>                 |                                                 |                                   |           |            |      |

| $V_{I,DIFF}$                                                           | Differential input voltage swing <sup>(2)</sup> |                                   | 0.15      | 1.3        | V    |

| $V_{ICM}$                                                              | Input common-mode voltage <sup>(3)</sup>        |                                   | 0.5       | VDD – 0.85 | V    |

| <b>AC Characteristic (PRI_IN, SEC_IN)</b>                              |                                                 |                                   |           |            |      |

| $f_{IN}$                                                               | Input frequency                                 |                                   | DC        | 200        | MHz  |

| idc                                                                    | Input duty cycle                                |                                   | 40%       | 60%        |      |

(1) PRI/SEC\_INN biased to VDD / 2

(2)  $V_{IL}$  should not be less than -0.3 V

(3) Input common-mode voltage is defined as  $V_{IH}$  (see [Figure 19](#)).

## CRYSTAL CHARACTERISTICS

over recommended ranges of supply voltage, load and ambient temperature (unless otherwise noted)

| PARAMETER                          | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|------------------------------------|-----------------|-----|-----|-----|------|

| Equivalent series resistance (ESR) |                 |     | 50  |     | Ω    |

| Maximum shunt capacitance          |                 |     | 7   |     | pF   |

| Drive level                        |                 |     | 100 |     | μW   |

## CRYSTAL OSCILLATOR CHARACTERISTICS

over recommended ranges of supply voltage, load and ambient temperature (unless otherwise noted)

| PARAMETER                                  | TEST CONDITIONS | MIN | TYP         | MAX | UNIT |

|--------------------------------------------|-----------------|-----|-------------|-----|------|

| Mode of oscillation                        |                 |     | Fundamental |     |      |

| Frequency                                  |                 | 8   | 50          | MHz |      |

| Frequency in overdrive mode <sup>(1)</sup> |                 |     | 50          | MHz |      |

| Frequency in bypass mode <sup>(2)</sup>    |                 |     | 50          | MHz |      |

| On-chip load capacitance                   |                 |     | 12          |     | pF   |

(1) Input signal swing (max) = 2 V; input signal  $t_r$  (max) = 10 ns;  $t_f$ (max) = 10 ns; functional, but device may not need ac parameters.

(2) Input signal swing (max) =  $V_{DD}$ ; input signal  $t_r$  (max) = 10 ns;  $t_f$ (max) = 10 ns; functional, but device may not need ac parameters.

## LVC MOS OUTPUT CHARACTERISTICS

over recommended ranges of supply voltage ( $V_{DDO} \leq VDD$ ), load ( $50 \Omega$  to  $V_{DDO}/2$ ), and ambient temperature (unless otherwise noted)

| PARAMETER                                               | TEST CONDITIONS                                               | MIN   | TYP   | MAX | UNIT |

|---------------------------------------------------------|---------------------------------------------------------------|-------|-------|-----|------|

| $f_{OUT}$                                               |                                                               |       |       | 200 | MHz  |

| $V_{OH}$<br>Output high voltage                         | $V_{DDO} = 3.135 \text{ V to } 3.465 \text{ V}$               | 0.8 * |       |     | V    |

|                                                         | $V_{DDO} = 2.375 \text{ V to } 2.625 \text{ V}$               | 0.8 * |       |     |      |

|                                                         | $V_{DDO} = 1.6 \text{ V to } 2 \text{ V}$                     | 0.7 * |       |     |      |

|                                                         | $V_{DDO} = 1.35 \text{ V to } 1.65 \text{ V}$                 | 0.7 * |       |     |      |

| $V_{OL}$<br>Output low voltage                          | $V_{DDO} = 3.135 \text{ V to } 3.465 \text{ V}$               |       | 0.2 * |     | V    |

|                                                         | $V_{DDO} = 2.375 \text{ V to } 2.625 \text{ V}$               |       | 0.2 * |     |      |

|                                                         | $V_{DDO} = 1.6 \text{ V to } 2 \text{ V}$                     |       | 0.3 * |     |      |

|                                                         | $V_{DDO} = 1.35 \text{ V to } 1.65 \text{ V}$                 |       | 0.3 * |     |      |

| $R_{OUT}$<br>Output impedance                           | $V_{DDO} = 3.3 \text{ V}$                                     |       | 15    |     | Ω    |

|                                                         | $V_{DDO} = 2.5 \text{ V}$                                     |       | 20    |     |      |

|                                                         | $V_{DDO} = 1.8 \text{ V}$                                     |       | 25    |     |      |

|                                                         | $V_{DDO} = 1.5 \text{ V}$                                     |       | 30    |     |      |

| $t_{SLEW-RATE}$<br>Output slew rate, rising and falling | $V_{DDO}=3.3\text{V} \pm/5\%, 20\% \text{ to } 80\%$          | 5.6   | 7.3   | 9.0 | V/ns |

|                                                         | $V_{DDO}=2.5\text{V} \pm/5\%, 20\% \text{ to } 80\%$          | 3.9   | 4.8   | 5.4 |      |

|                                                         | $V_{DDO}=1.8\text{V} \pm/200\text{mV}, 20\% \text{ to } 80\%$ | 1.6   | 2.1   | 2.5 |      |

|                                                         | $V_{DDO}=1.5\text{V} \pm/150\text{mV}, 20\% \text{ to } 80\%$ | 0.9   | 1.2   | 1.4 |      |

| $t_{SK}$                                                | Output skew                                                   |       | 30    | 50  | ps   |

| $t_{SK,PP}$                                             | Part-to-part skew <sup>(1)</sup>                              |       |       | 2   | ns   |

(1) Calculation for part-to-part skew is the difference between the fastest and the slowest  $t_{pd}$  across multiple devices.

## LVC MOS OUTPUT CHARACTERISTICS (continued)

over recommended ranges of supply voltage ( $V_{DDO} \leq VDD$ ), load ( $50 \Omega$  to  $VDD/2$ ), and ambient temperature (unless otherwise noted)

| PARAMETER                                                 | TEST CONDITIONS                                                                                                                                                     | MIN                                                          | TYP  | MAX | UNIT        |

|-----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|------|-----|-------------|

| $t_{DELAY}$<br>Output frequency                           | $VDD = 3.3 \text{ V} \pm 5\%$ ,<br>$VDDO = 1.35 \text{ V}$ to $VDD$                                                                                                 | 1.5                                                          | 1.95 | 4.0 | ns          |

|                                                           | $VDD = 2.5 \text{ V} \pm 5\%$ ,<br>$VDDO = 1.35 \text{ V}$ to $VDD$                                                                                                 | 1.8                                                          | 2.4  | 4.4 |             |

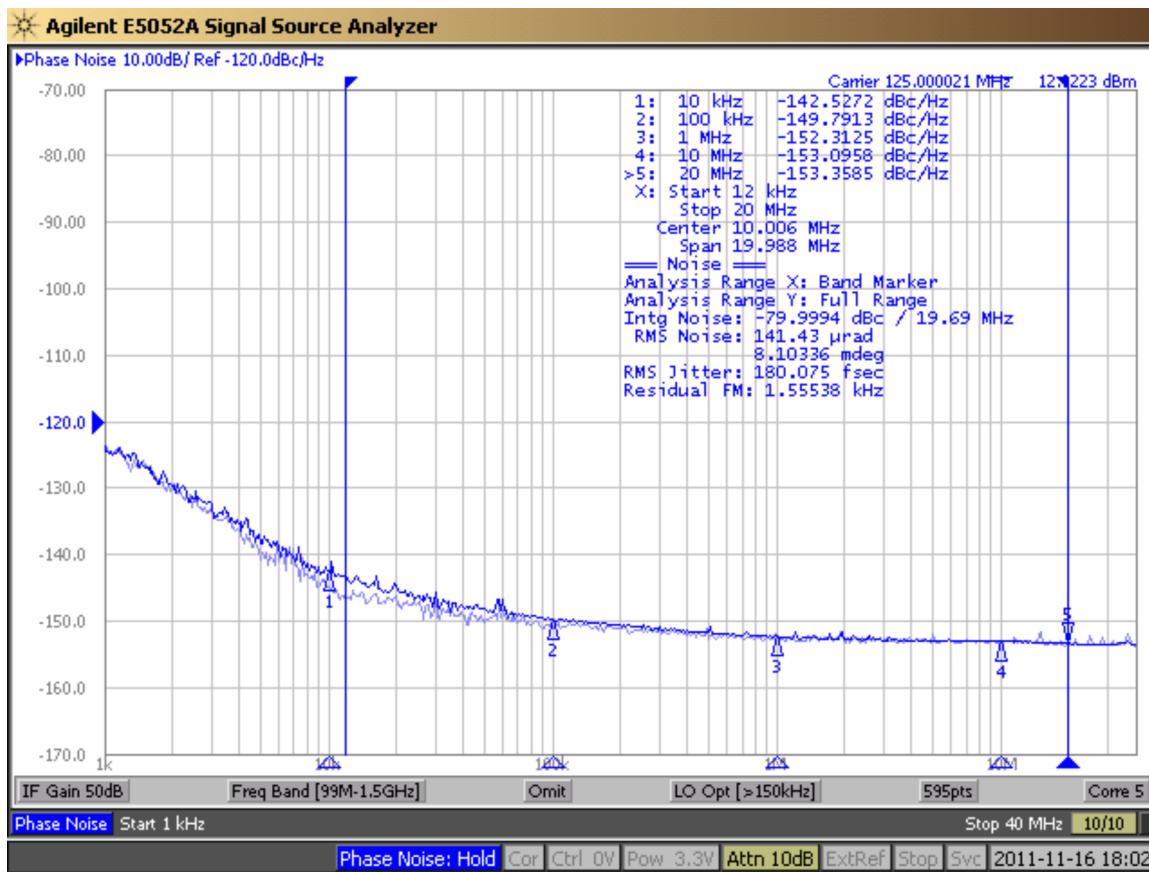

| $t_{RJIT}$<br>System-level additive jitter <sup>(2)</sup> | Single-ended input, $VDD = 3.3 \text{ V}$ ,<br>$VDDO = 3.3 \text{ V}$                                                                                               | 25                                                           |      |     | $f_S$ , RMS |

|                                                           | Single-ended input, $VDD = 2.5 \text{ V}$ or<br>$3.3 \text{ V}$ , $VDDO = 1.5 \text{ V}$ , $1.8 \text{ V}$ , or $2.5 \text{ V}$ ,<br>$f_{IN/OUT} = 125 \text{ MHz}$ |                                                              | 30   |     |             |

|                                                           | Differential input, $VDD = 3.3 \text{ V}$ ,<br>$VDDO = 3.3 \text{ V}$                                                                                               |                                                              | 30   |     |             |

|                                                           | Differential input, $VDD = 2.5 \text{ V}$ or<br>$3.3 \text{ V}$ , $VDDO = 1.5 \text{ V}$ , $1.8 \text{ V}$ , or $2.5 \text{ V}$ ,<br>$f_{IN/OUT} = 125 \text{ MHz}$ |                                                              | 30   |     |             |

| $NF$<br>Noise floor                                       | 10-kHz offset <sup>(3)</sup>                                                                                                                                        |                                                              | –145 |     | dBc/Hz      |

|                                                           | 100-kHz offset <sup>(3)</sup>                                                                                                                                       |                                                              | –156 |     |             |

|                                                           | 1-MHz offset <sup>(3)</sup>                                                                                                                                         |                                                              | –163 |     |             |

|                                                           | 10-MHz offset <sup>(3)</sup>                                                                                                                                        |                                                              | –164 |     |             |

|                                                           | 20-MHz offset <sup>(3)</sup>                                                                                                                                        |                                                              | –164 |     |             |

|                                                           | 10-kHz offset <sup>(4)</sup>                                                                                                                                        |                                                              | –145 |     |             |

|                                                           | 100-kHz offset <sup>(4)</sup>                                                                                                                                       |                                                              | –155 |     |             |

|                                                           | 1-MHz offset <sup>(4)</sup>                                                                                                                                         |                                                              | –160 |     |             |

|                                                           | 10-MHz offset <sup>(4)</sup>                                                                                                                                        |                                                              | –161 |     |             |

|                                                           | 20-MHz offset <sup>(4)</sup>                                                                                                                                        |                                                              | –162 |     |             |

| $odc$                                                     | Output duty cycle                                                                                                                                                   | $f_{IN/OUT} = 125 \text{ MHz}$ , $idc = 50\%$ <sup>(5)</sup> | 45%  | 55% |             |

| $t_{EN}$                                                  | Output enable or disable time                                                                                                                                       |                                                              |      | 2   | Cycle       |

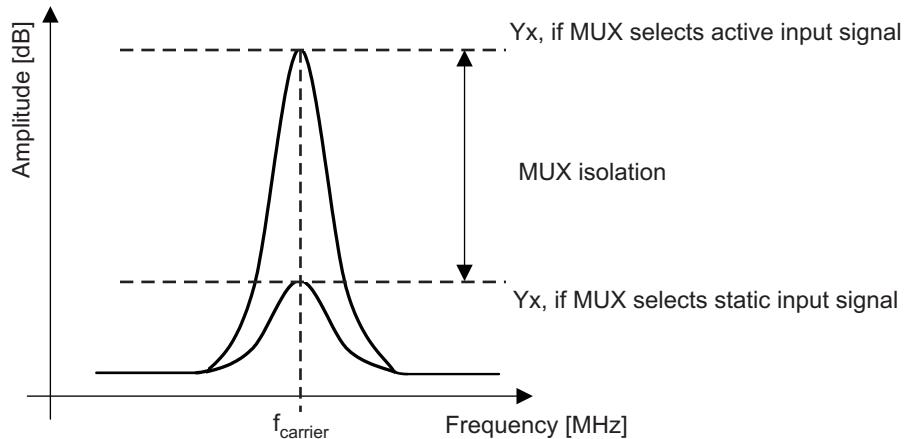

| $MUX_{ISOLATION}$                                         | MUX isolation <sup>(6)</sup>                                                                                                                                        | 125 MHz                                                      | 55   |     | dB          |

(2) Integration range: 12 kHz–20 MHz; input source see the [System-Level Additive-Jitter Measurement](#) section

(3) Single-ended input,  $f_{IN/OUT} = 125 \text{ MHz}$ ,  $VDD = VDDO = 3.3 \text{ V}$

(4) Differential input,  $f_{IN/OUT} = 125 \text{ MHz}$ ,  $VDD = VDDO = 3.3 \text{ V}$

(5) Stable  $V_{IH}$ ,  $V_{IL}$ , and  $V_{CM}$

(6) See [Figure 18](#).

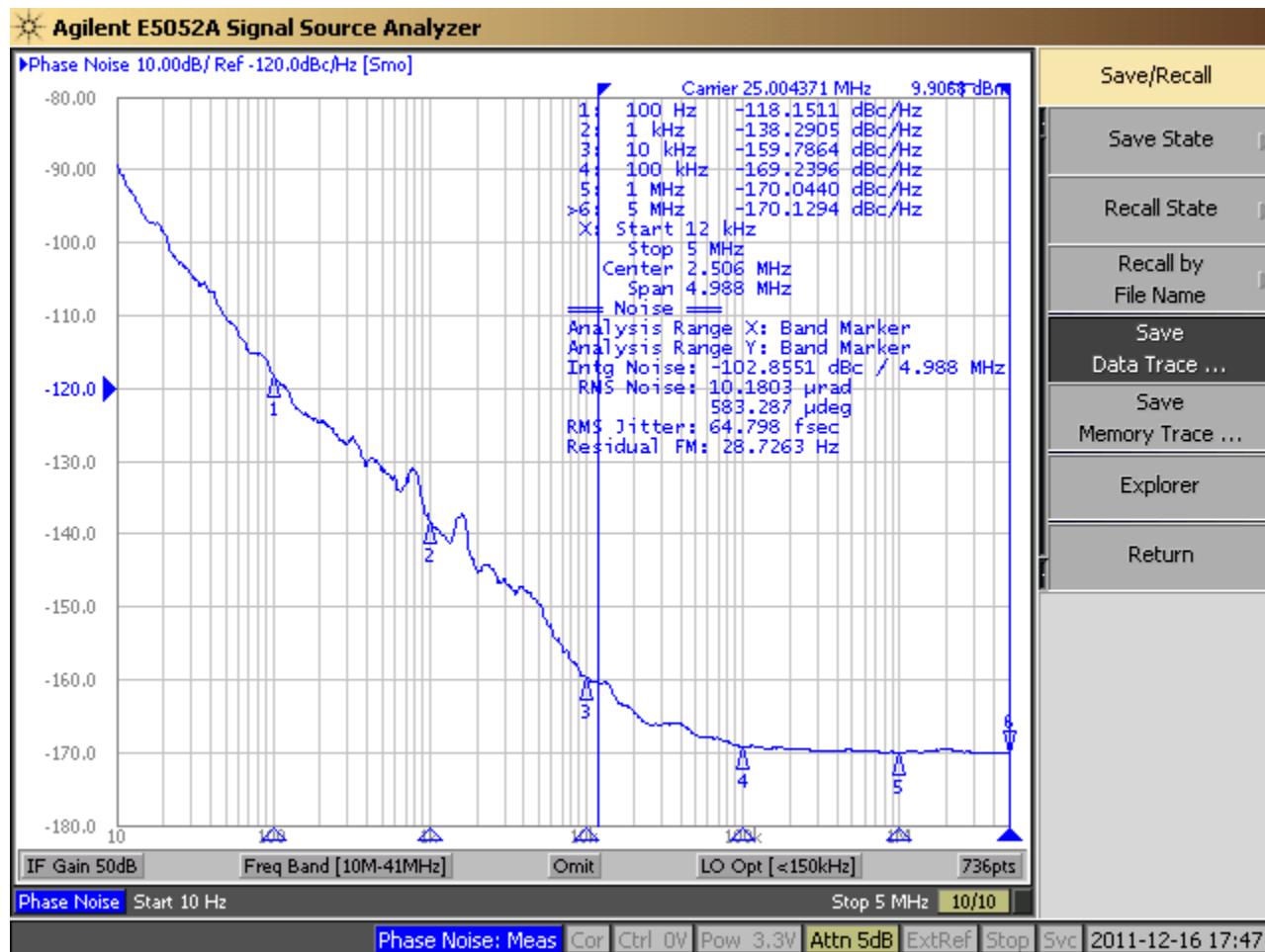

## PHASE NOISE WITH XTAL<sup>(1)</sup> SELECTED

VDD = VDDO = 2.5 V or 3.3 V, f<sub>XTAL</sub> = 25 MHz, T<sub>A</sub> = 25°C (unless otherwise noted)

| PARAMETER |                                              | TEST CONDITIONS                                   | MIN | TYP  | MAX | UNIT   |

|-----------|----------------------------------------------|---------------------------------------------------|-----|------|-----|--------|

| Jrms      | RMS phase jitter                             | IB = 12 kHz to 5 MHz, VDD = VDDO = 3.3 V          |     | 80   |     | fs rms |

|           |                                              | IB = 12 kHz to 5 MHz, VDD = VDDO = 2.5 V          |     | 115  |     |        |

| PN        | Phase noise (see <a href="#">Figure 15</a> ) | f <sub>offset</sub> = 100 Hz, VDD = VDDO = 3.3 V  |     | -92  |     | dBc/Hz |

|           |                                              | f <sub>offset</sub> = 1 kHz, VDD = VDDO = 3.3 V   |     | -137 |     |        |

|           |                                              | f <sub>offset</sub> = 10 kHz, VDD = VDDO = 3.3 V  |     | -163 |     |        |

|           |                                              | f <sub>offset</sub> = 100 kHz, VDD = VDDO = 3.3 V |     | -168 |     |        |

|           |                                              | f <sub>offset</sub> = 1 MHz, VDD = VDDO = 3.3 V   |     | -168 |     |        |

|           |                                              | f <sub>offset</sub> = 5 MHz, VDD = VDDO = 3.3 V   |     | -169 |     |        |

|           |                                              | f <sub>offset</sub> = 100 Hz, VDD = VDDO = 2.5 V  |     | -91  |     |        |

|           |                                              | f <sub>offset</sub> = 1 kHz, VDD = VDDO = 2.5 V   |     | -136 |     |        |

|           |                                              | f <sub>offset</sub> = 10 kHz, VDD = VDDO = 2.5 V  |     | -159 |     |        |

|           |                                              | f <sub>offset</sub> = 100 kHz, VDD = VDDO = 2.5 V |     | -164 |     |        |

|           |                                              | f <sub>offset</sub> = 1 MHz, VDD = VDDO = 2.5 V   |     | -165 |     |        |

|           |                                              | f <sub>offset</sub> = 5 MHz, VDD = VDDO = 2.5 V   |     | -165 |     |        |

(1) Crystal specification: C<sub>L</sub> = 18 pF; ESR = 35 Ω (max); C<sub>0</sub> = 7 pF; drive level = 100 μW (max)

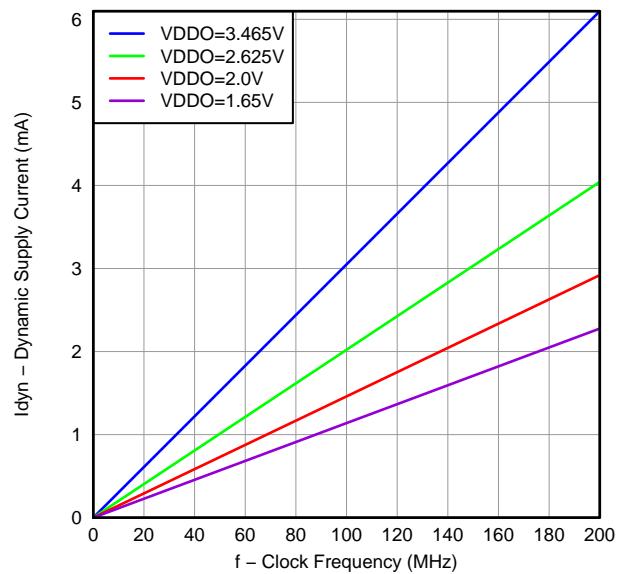

## DEVICE CURRENT CONSUMPTION

over recommended ranges of supply voltage, load and ambient temperature (unless otherwise noted)

| PARAMETER                                  |                                                         | TEST CONDITIONS                                                                                                                                       | MIN | TYP | MAX | UNIT |

|--------------------------------------------|---------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| <b>OVERALL PARAMETERS FOR ALL VERSIONS</b> |                                                         |                                                                                                                                                       |     |     |     |      |

| I <sub>DD</sub>                            | Static device current <sup>(1)</sup>                    | OE = 0 V or V <sub>DD</sub> ;<br>Ref. input (PRI/SEC) = 0 V or V <sub>DD</sub> ;<br>I <sub>O</sub> = 0 mA; V <sub>DD</sub> / V <sub>DDO</sub> = 3.3 V |     | 14  |     | mA   |

|                                            |                                                         | OE = 0 V or V <sub>DD</sub> ;<br>Ref. input (PRI/SEC) = 0 V or V <sub>DD</sub> ;<br>I <sub>O</sub> = 0 mA; V <sub>DD</sub> / V <sub>DDO</sub> = 2.5 V |     | 8   |     |      |

| I <sub>DD,XTAL</sub>                       | Device current with XTAL input <sup>(1)</sup>           |                                                                                                                                                       |     | 20  |     | mA   |

| C <sub>PD</sub>                            | Power dissipation capacitance per output <sup>(2)</sup> | VDDO = 3.465 V; f = 100 MHz                                                                                                                           |     | 8.8 |     | pF   |

|                                            |                                                         | VDDO = 2.625 V; f = 100 MHz                                                                                                                           |     | 7.7 |     |      |

|                                            |                                                         | VDDO = 2 V; f = 100 MHz                                                                                                                               |     | 7.3 |     |      |

|                                            |                                                         | VDDO = 1.65 V; f = 100 MHz                                                                                                                            |     | 6.9 |     |      |

(1) I<sub>DD</sub> and I<sub>DD,XTAL</sub> is the current through V<sub>DD</sub>; outputs enabled or in the high-impedance state; no load.

(2) This is the formula for the power dissipation calculation (see the [Power Considerations](#) section)

$$I_{DD,Total} = I_{DD} + I_{DD,Cload} + I_{DD,dyn} \text{ [mA]}$$

$$I_{DD,dyn} = C_{PD} \times V_{DDO} \times f \times n \text{ [mA]}$$

$$I_{DD,Cload} = C_{load} \times V_{DDO} \times f \times n \text{ [mA]}$$

n = Number of switching output pins

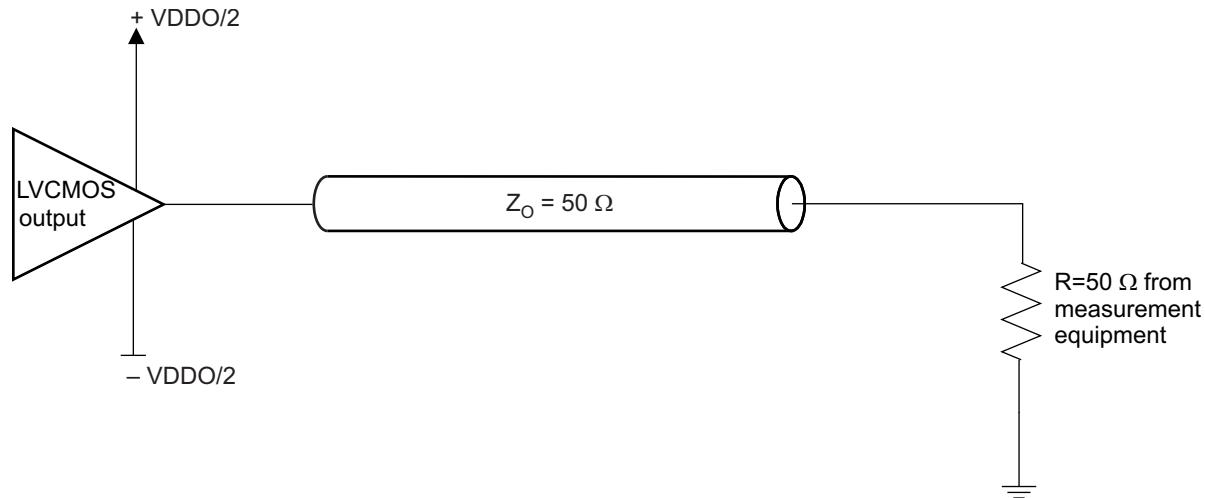

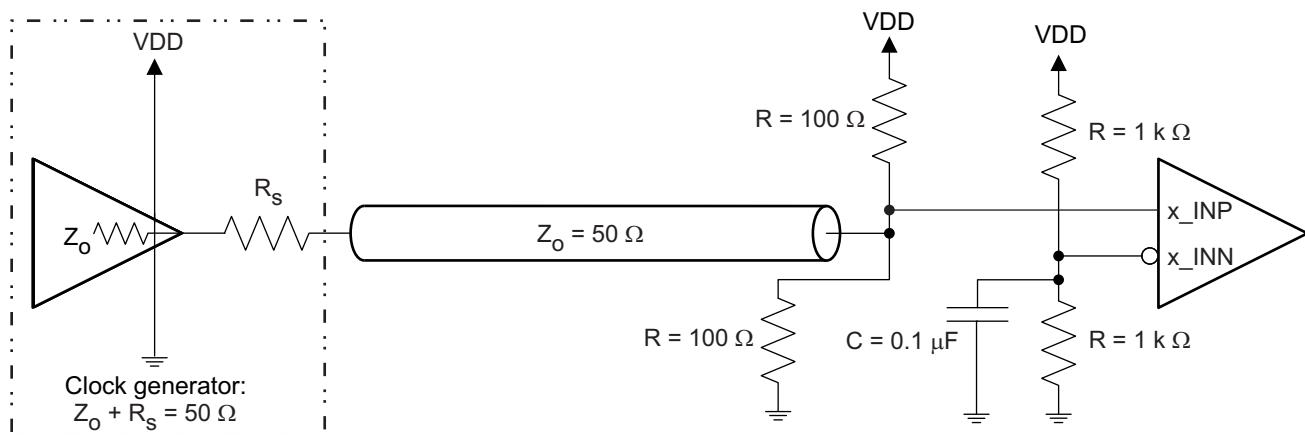

## TEST CONFIGURATIONS

Figure 2 through Figure 8 illustrate how to set up the device for a variety of test configurations.

**Figure 2. LVCMOS Output DC Configuration; Test Load Circuit**

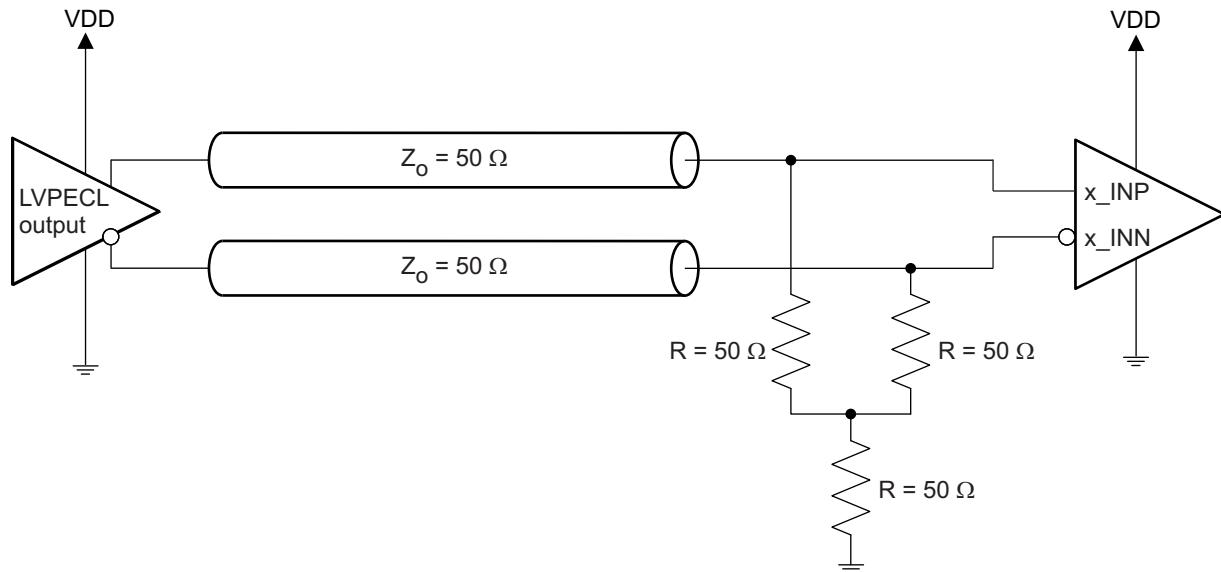

**Figure 3. LVCMOS Input DC Configuration During Device Test**

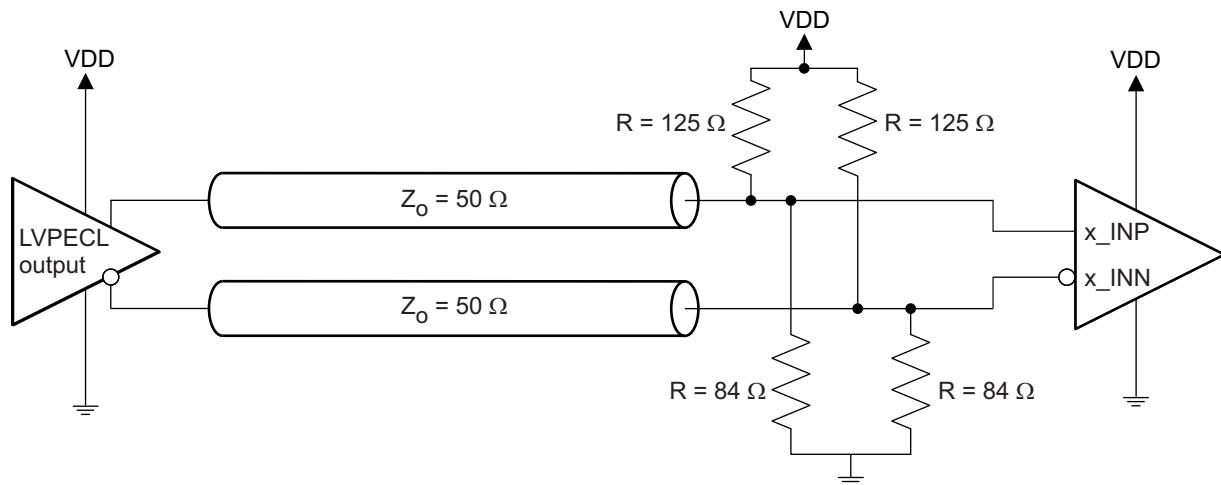

**Figure 4. LVPECL Input Configuration During Device Test**

**Figure 5. LVPECL Input Configuration During Device Test**

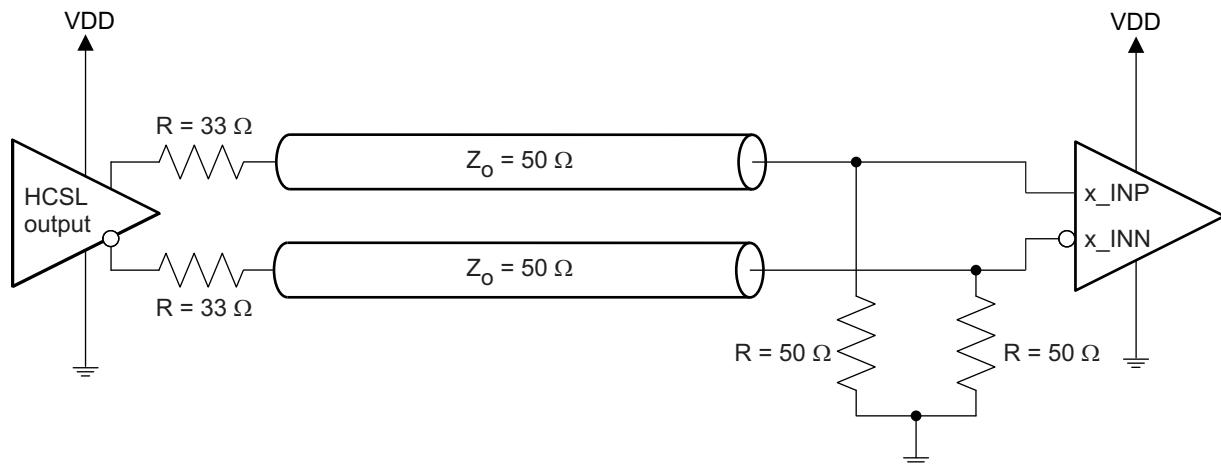

**Figure 6. HCSL Input Configuration During Device Test**

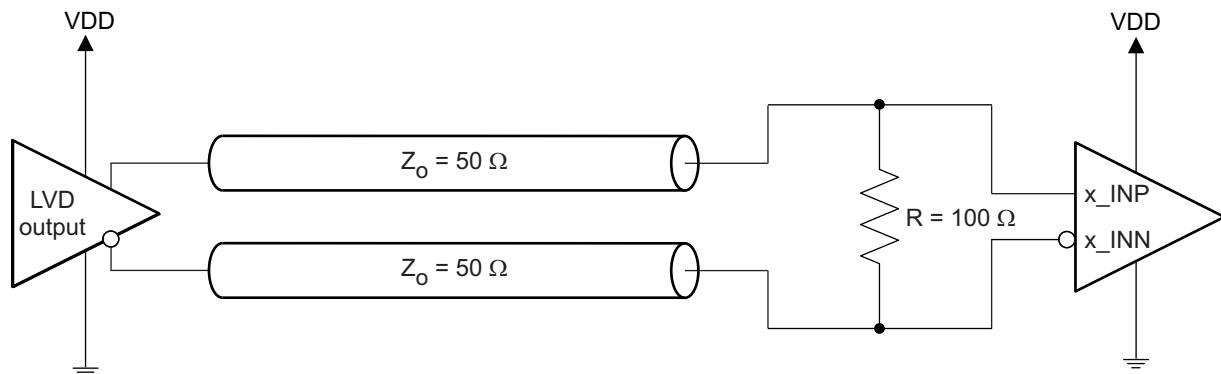

**Figure 7. LVDS Input Configuration During Device Test**

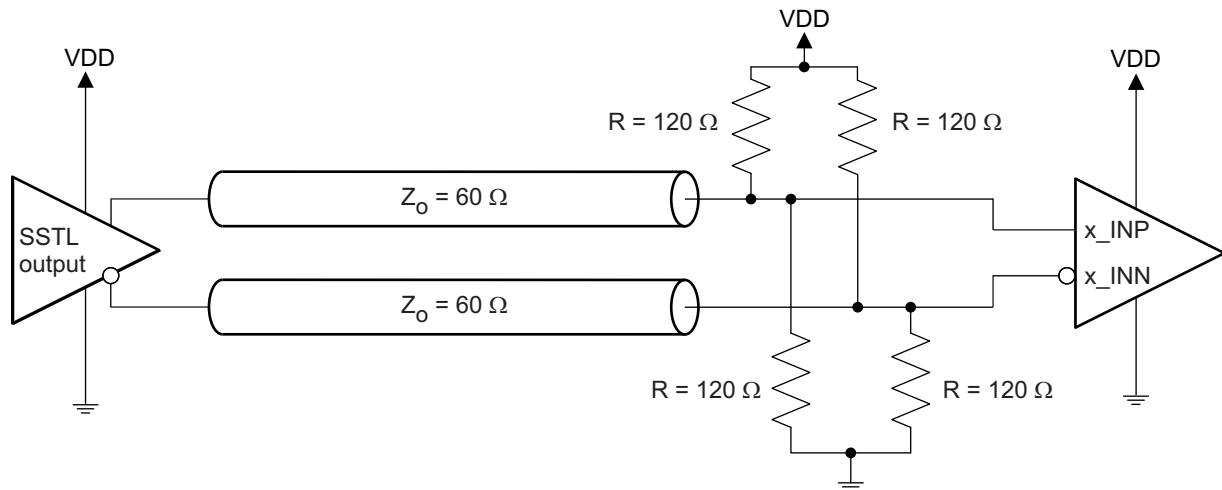

Figure 8. SSTL Input Configuration During Device Test

## APPLICATION INFORMATION

### Typical Application Load

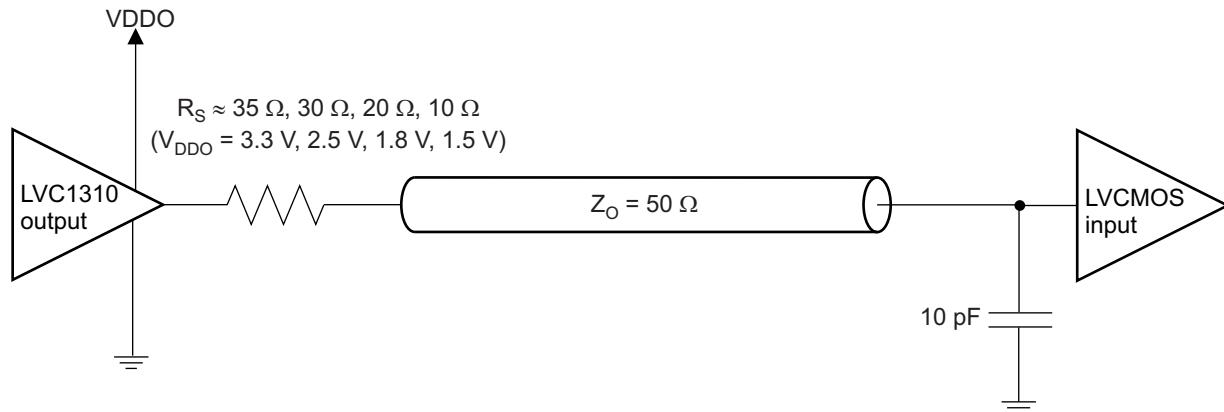

**Figure 9. LVC1310 Output DC Configuration: Typical Application Load**

### Parameter Measurement Information

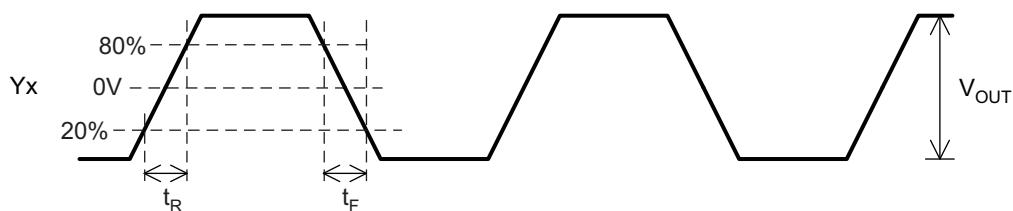

**Figure 10. LVC1310 Output Voltage, and Rise and Fall Times**

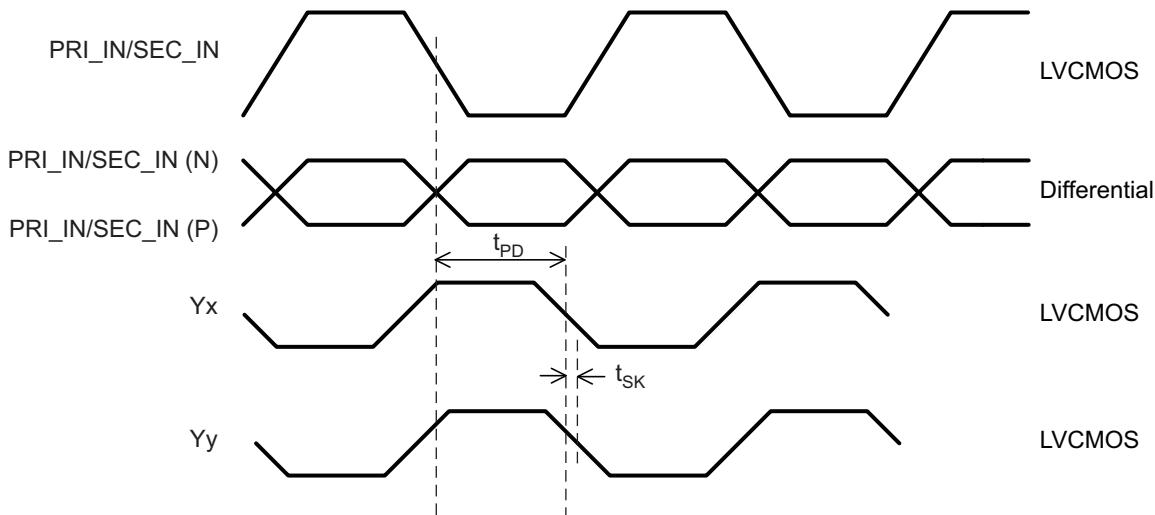

**Figure 11. Differential and Single-Ended Output Skew and Propagation Delay**

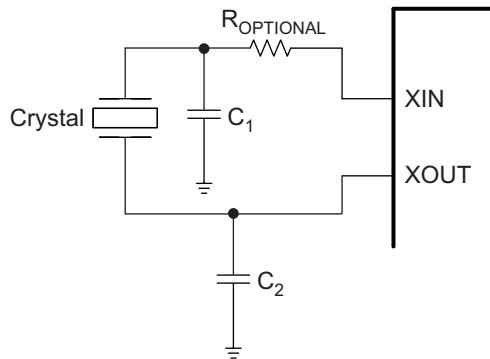

### Crystal Oscillator Input

The crystal oscillator circuit is characterized with 18-pF parallel-resonant crystals. Choices of C1 and C2 were to minimize the ppm error. Optional resistor  $R_{OPTIONAL}$  limits the drive level of the oscillator circuit.

Figure 12. Crystal Reference Input

The input XIN can accept single-ended LVCMS signals in two configurations. It is possible to overdrive the oscillator stage or to use a pure LVCMS input (see [Table 1](#)). If overdriving the oscillator stage, it is necessary to ac-couple the input with a capacitor (see [Figure 13](#)). Otherwise, if selecting the bypass, there is no requirement for a coupling capacitor. Additional measurements and information about crystal oscillator input and limiting the drive level are available in the applications report *Crystal Oscillator Performance of the CDCLVC1310 (SCAA119)*.

**NOTE**

If using the overdrive or bypass mode, the device is functional, but may not meet its ac parameters.

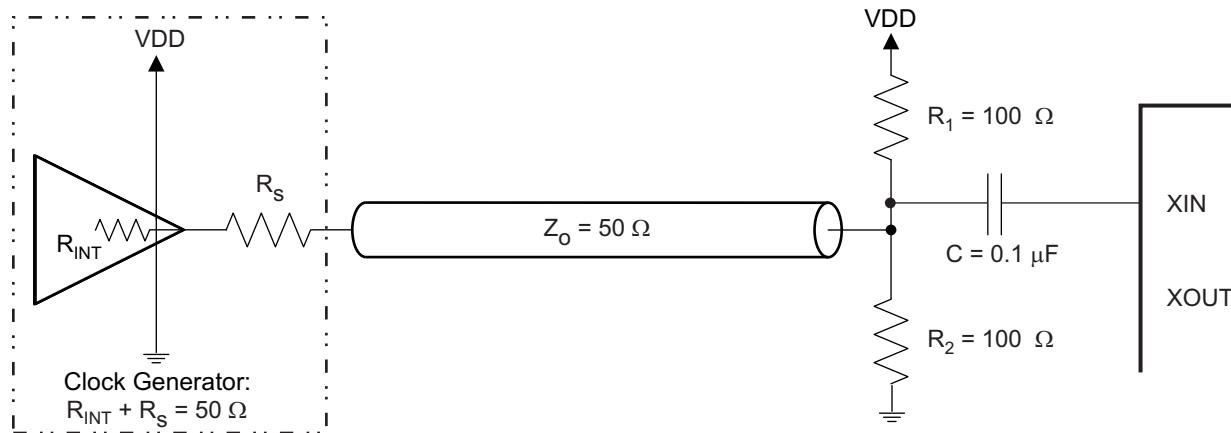

Figure 13. Single-Ended Crystal Input

### Phase-Noise Performance

The CDCLVC1310 provides ultralow phase-noise outputs (noise floor =  $-170$  dBc/Hz) if it has an attached crystal. [Figure 14](#) shows the phase-noise plot of the CDCLVC1310 with a 25-MHz crystal at  $V_{DD} = V_{DDO} = 3.3$  V and room temperature.

**Figure 14. Phase-Noise Profile With 25-MHz Crystal at Nominal Conditions**

### System-Level Additive-Jitter Measurement

For high-performance devices, limitations of the equipment influence phase-noise measurements. The noise floor of the equipment often exceeds the noise floor of the device. The real noise floor of the device is probably lower (see [LVC MOS Output Characteristics](#)). Phase noise is influenced by the input source and the measurement equipment. Additional measurements and information about system-level additive jitter and noise floor are available in the applications report *Phase Noise Performance of CDCLVC1310* ([SCAA115](#)).

Figure 15. Input Phase Noise (179.4 fs, Light Blue) and Output Phase Noise (180 fs, Dark Blue)

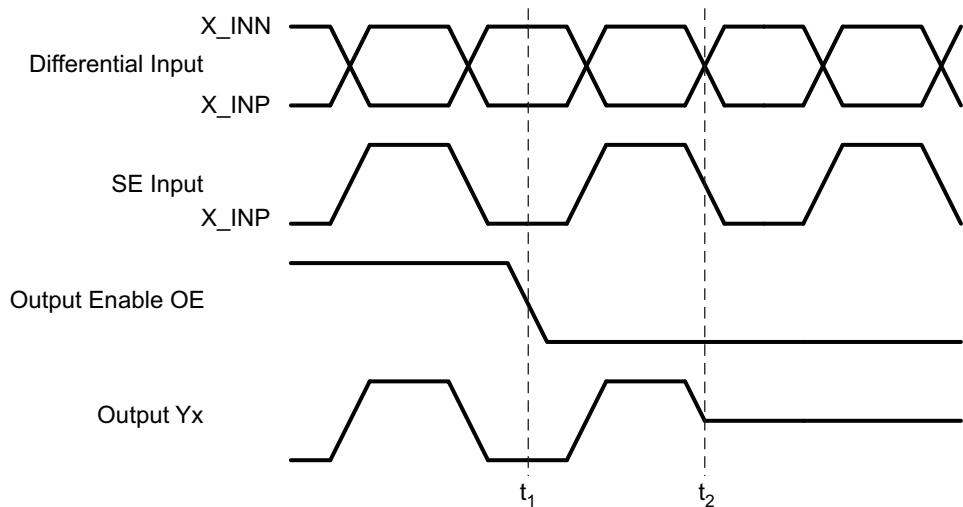

### Output Enable

Pulling OE to LOW ( $t_1$ ), forces the outputs to the high-impedance state after the next falling edge of the input signal ( $t_2$ ). The outputs remain in the high-impedance state as long as OE is LOW (see Figure 16).

Figure 16. OE: Disable Outputs

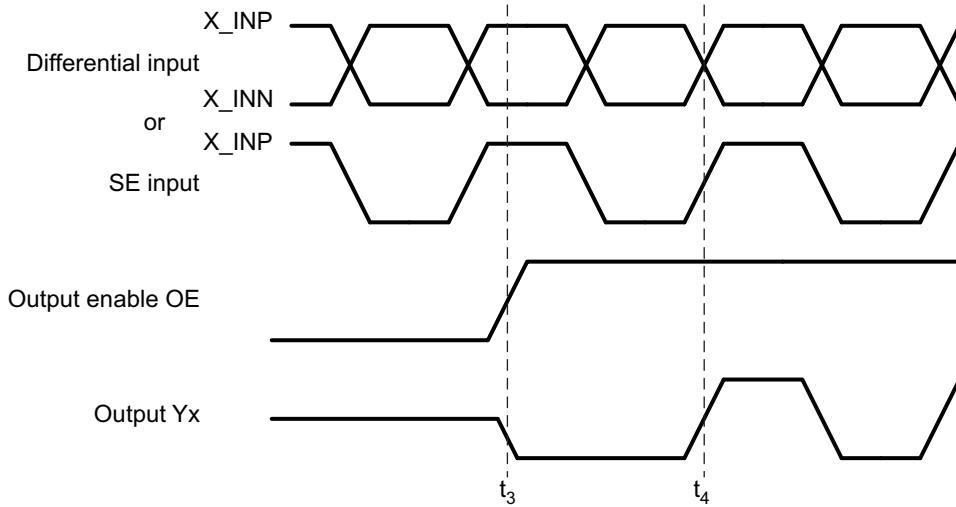

If the outputs are in the high-impedance state, pulling OE to HIGH forces all outputs LOW asynchronously ( $t_3$ ). Within two clock cycles (maximum), the outputs start switching again ( $t_4$ ), after a falling edge of the input signal (see [Figure 17](#)).

**Figure 17. OE: Enable Outputs**

If the outputs are in the high-impedance state and the input is static (no clock signal), OE works fully asynchronously. A transition of OE from LOW to HIGH forces the outputs to LOW. A transition from HIGH to LOW does not force the high-impedance state again. Therefore, a state change requires a falling edge of the input signal (see [Figure 16](#)).

## MUX Isolation

The definition of MUX isolation is the difference in output amplitude (dB) between an active and a static input signal.

**Figure 18. Output Spectrum of an Active and a Static Input Signal**

## Differential Input Level

NOTE: The calculation for VCM is:  $V_{CM} = V_{DD} - V_{ICM} - V_{I,DIFF}/2$

**Figure 19. Differential Input Level**

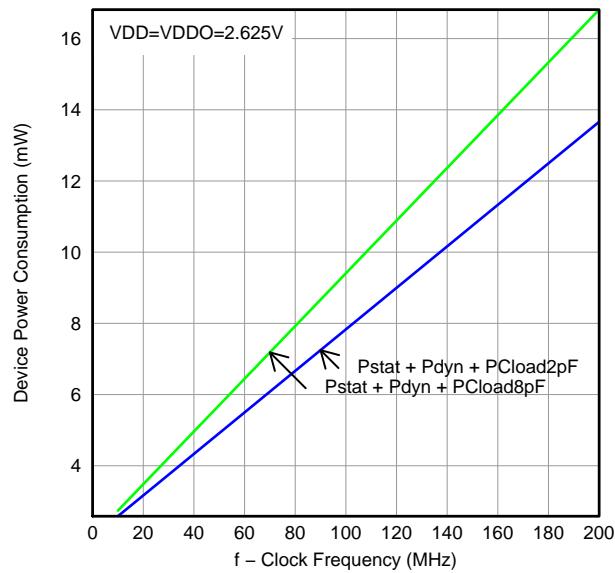

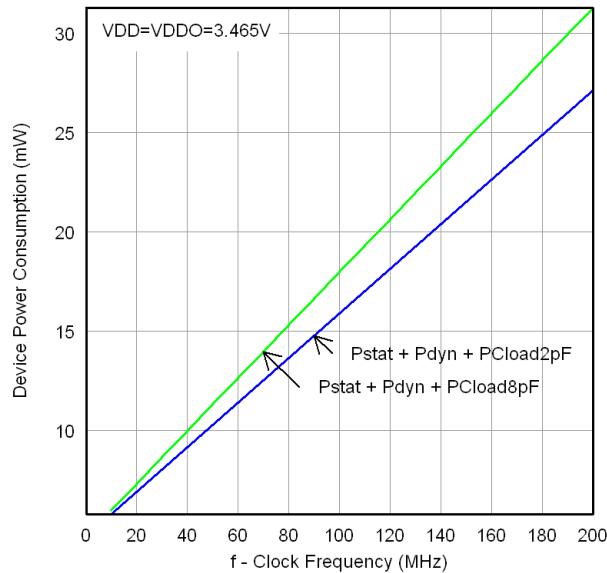

## Power Considerations

The following power consideration refers to the device-consumed power consumption only. The device power consumption is the sum of static power and dynamic power. The dynamic power usage consists of two components:

- Power used by the device as it switches states

- Power required to charge any output load

The output load can be capacitive-only or capacitive and resistive. Use the following formula to calculate the power consumption of the device:

$$P_{Dev} = P_{stat} + P_{dyn} + P_{Cload} \text{ (see Figure 20 and Figure 21)}$$

$$P_{stat} = I_{DD} \times V_{DD}$$

$$P_{dyn} + P_{Cload} = (I_{DD,dyn} + I_{DD,Cload}) \times V_{DDO}$$

where:

$$I_{DD,dyn} = C_{PD} \times V_{DDO} \times f \times n \text{ [mA] (see Figure 22)}$$

$$I_{DD,Cload} = C_{load} \times V_{DDO} \times f \times n \text{ [mA]}$$

Example for power consumption of the CDCLVC1310: 10 outputs are switching,  $f = 100$  MHz,  $V_{DD} = V_{DDO} = 3.3$  V and assuming  $C_{load} = 2$  pF per output:

$$P_{Dev} = 46.2 \text{ mW} + 117.5 \text{ mW} = 163.7 \text{ mW}$$

$$P_{stat} = 14 \text{ mA} \times 3.3 \text{ V} = 46.2 \text{ mW}$$

$$P_{dyn} + P_{Cload} = (29 \text{ mA} + 6.6 \text{ mA}) \times 3.3 \text{ V} = 117.5 \text{ mW}$$

$$I_{DD,dyn} = 8.8 \text{ pF} \times 3.3 \text{ V} \times 100 \text{ MHz} \times 10 = 29 \text{ mA}$$

$$I_{DD,Cload} = 2 \text{ pF} \times 3.3 \text{ V} \times 100 \text{ MHz} \times 10 = 6.6 \text{ mA}$$

### NOTE

For dimensioning the power supply, consider the total power consumption. The total power consumption is the sum of device power consumption and the power consumption of the load.

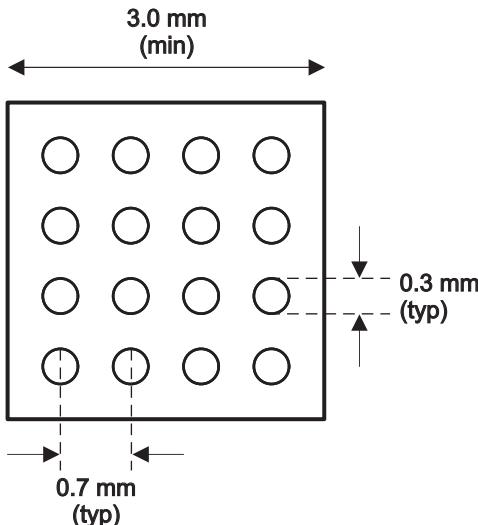

## Thermal Management

Power consumption of the CDCLVC1310 can be high enough to require attention to thermal management. For reliability and performance reasons, limit the die temperature to a maximum of 125°C. That is, as an estimate,  $T_A$  (ambient temperature) plus device power consumption times  $\theta_{JA}$  should not exceed 125°C.

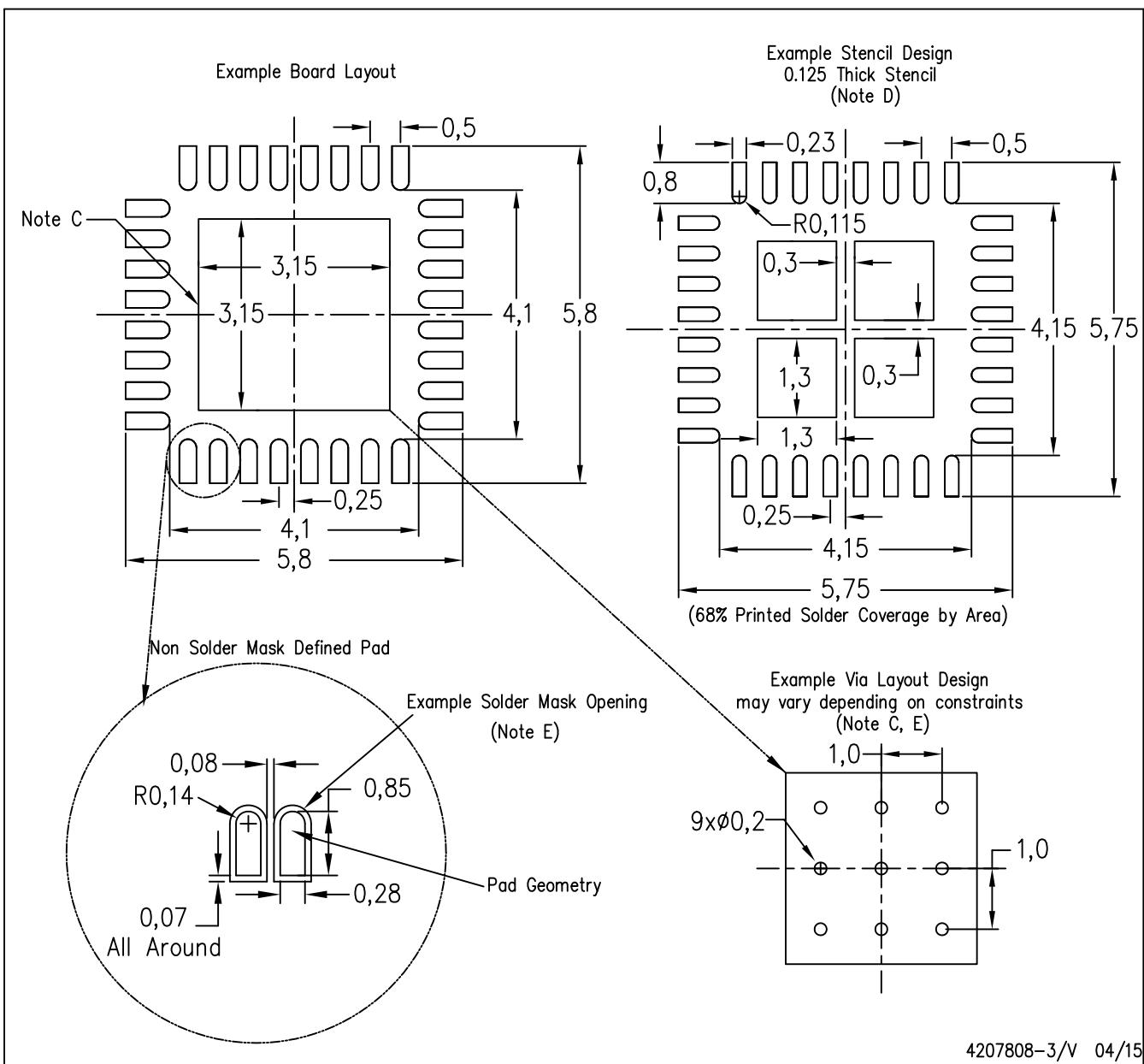

The device package has an exposed pad that provides the primary heat removal path as well as an electrical grounding to the printed circuit board (PCB). To maximize the removal of heat from the package, incorporate a thermal landing pattern including multiple vias to a ground plane on the PCB within the footprint of the package. Solder the exposed pad down to ensure adequate heat conduction out of the package. [Figure 23](#) shows a recommended land and via pattern.

**Figure 23. Recommended PCB Layout for CDCLVC1310**

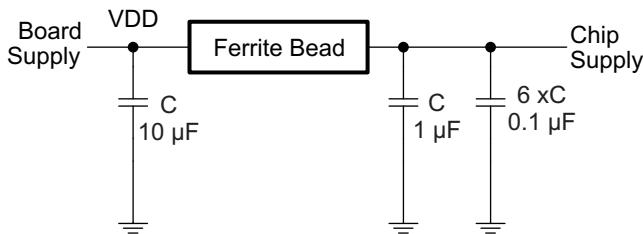

## Power-Supply Filtering

High-performance clock buffers are sensitive to noise on the power supply, which can dramatically increase the additive jitter of the buffer. Thus, it is essential to reduce noise from the system power supply, especially when jitter or phase noise is very critical to applications.

Use of filter capacitors eliminates the low-frequency noise from power supply, where the bypass capacitors provide the very low-impedance path for high-frequency noise and guard the power-supply system against induced fluctuations. The bypass capacitors also provide instantaneous current surges as required by the device, and should have low ESR. To use the bypass capacitors properly, place them very close to the power supply pins and lay out traces with short loops to minimize inductance. TI recommends to adding as many high-frequency (for example,  $0.1\text{-}\mu\text{F}$ ) bypass capacitors as there are supply pins in the package. There is a recommendation, but not a requirement, to insert a ferrite bead between the board power supply and the chip power supply to isolate the high-frequency switching noises generated by the clock driver, preventing them from leaking into the board supply. Choosing an appropriate ferrite bead with very low dc resistance is important, because it is imperative to provide adequate isolation between the board supply and the chip supply, and to maintain a voltage at the supply pins that is greater than the minimum voltage required for proper operation.

**Figure 24. Power-Supply Decoupling**

## REVISION HISTORY

|                                                                      | Page |

|----------------------------------------------------------------------|------|

| <b>Changes from Revision D (July 2013) to Revision E</b>             |      |

| • Changed $V_{OH}$ in LVC MOS OUTPUT CHARACTERISTICS .....           | 7    |

| • Changed $V_{OL}$ in LVC MOS OUTPUT CHARACTERISTICS .....           | 7    |

| • Changed $t_{SLEW-RATE}$ in LVC MOS OUTPUT CHARACTERISTICS .....    | 7    |

| <b>Changes from Revision C (October 2012) to Revision D</b>          |      |

| • Changed $t_{DELAY}$ in LVC MOS OUTPUT CHARACTERISTICS .....        | 8    |

| <b>Changes from Revision B (February 2012) to Revision C</b>         |      |

| • Changed unit for phase jitter from picosecond to femtosecond ..... | 9    |

| • Revised <a href="#">Figure 3</a> .....                             | 10   |

| • Revised <a href="#">Figure 4</a> .....                             | 10   |

| • Revised <a href="#">Figure 5</a> .....                             | 11   |

| • Revised <a href="#">Figure 6</a> .....                             | 11   |

| • Revised <a href="#">Figure 8</a> .....                             | 12   |

| • Added reference to application report SCAA119 .....                | 14   |

**PACKAGING INFORMATION**

| Orderable Device | Status<br>(1) | Package Type | Package Drawing | Pins | Package Qty | Eco Plan<br>(2)         | Lead/Ball Finish<br>(6) | MSL Peak Temp<br>(3) | Op Temp (°C) | Device Marking<br>(4/5) | Samples        |

|------------------|---------------|--------------|-----------------|------|-------------|-------------------------|-------------------------|----------------------|--------------|-------------------------|----------------|

| CDCLVC1310RHBR   | ACTIVE        | VQFN         | RHB             | 32   | 3000        | Green (RoHS & no Sb/Br) | CU NIPDAU               | Level-2-260C-1 YEAR  | -40 to 85    | CDCLVC 1310             | <b>Samples</b> |

(1) The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

**LIFEBUY:** TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

**NRND:** Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBsolete:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check <http://www.ti.com/productcontent> for the latest availability information and additional product content details.

**TBD:** The Pb-Free/Green conversion plan has not been defined.

**Pb-Free (RoHS):** TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

**Green (RoHS & no Sb/Br):** TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

(3) MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

(4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

(5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

(6) Lead/Ball Finish - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead/Ball Finish values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

www.ti.com

## PACKAGE OPTION ADDENDUM

24-Nov-2014

---

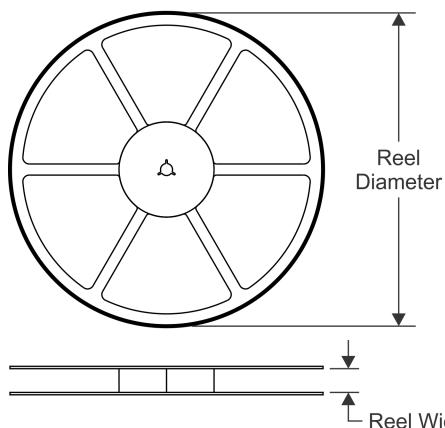

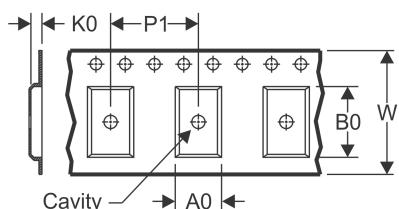

**TAPE AND REEL INFORMATION**

**REEL DIMENSIONS**

**TAPE DIMENSIONS**

|    |                                                           |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

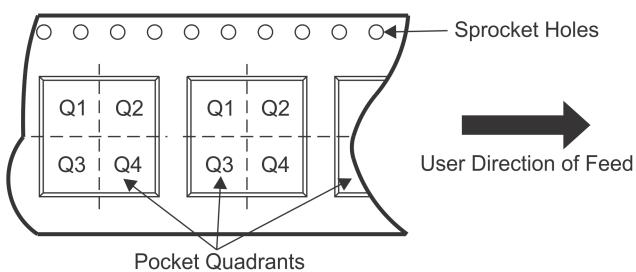

**QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE**

\*All dimensions are nominal

| Device         | Package Type | Package Drawing | Pins | SPQ  | Reel Diameter (mm) | Reel Width W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | Pin1 Quadrant |

|----------------|--------------|-----------------|------|------|--------------------|--------------------|---------|---------|---------|---------|--------|---------------|

| CDCLVC1310RHBR | VQFN         | RHB             | 32   | 3000 | 330.0              | 12.4               | 5.3     | 5.3     | 1.1     | 8.0     | 12.0   | Q2            |

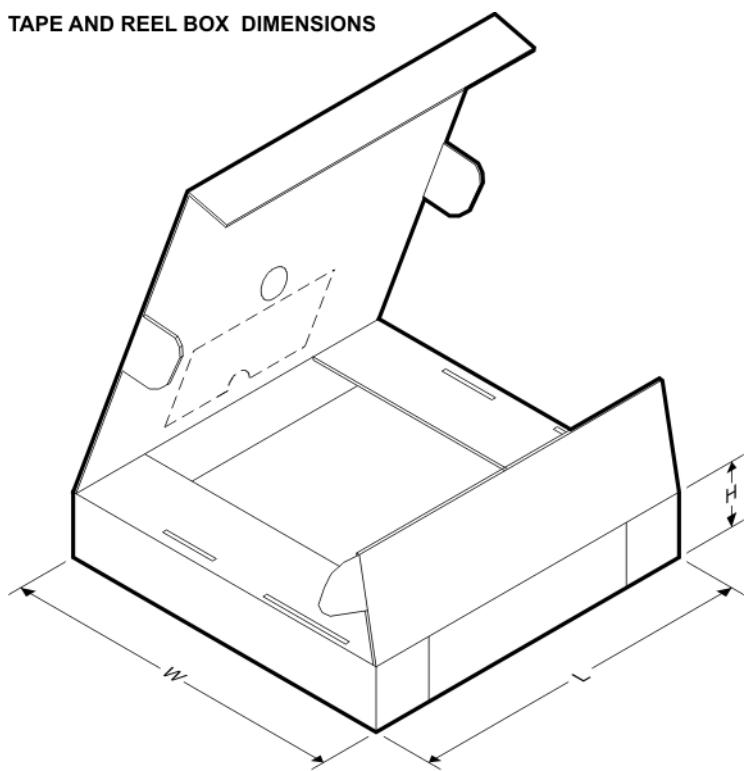

**TAPE AND REEL BOX DIMENSIONS**

\*All dimensions are nominal

| Device         | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|----------------|--------------|-----------------|------|------|-------------|------------|-------------|

| CDCLVC1310RHBR | VQFN         | RHB             | 32   | 3000 | 367.0       | 367.0      | 35.0        |

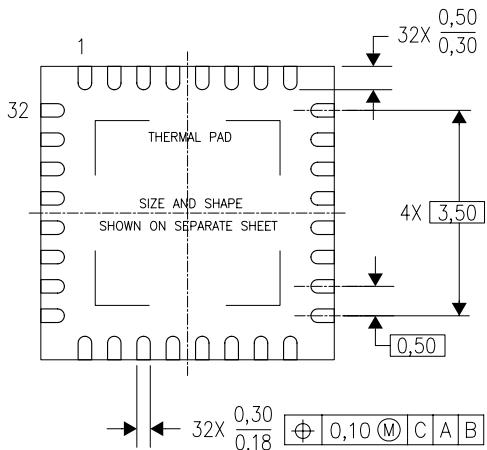

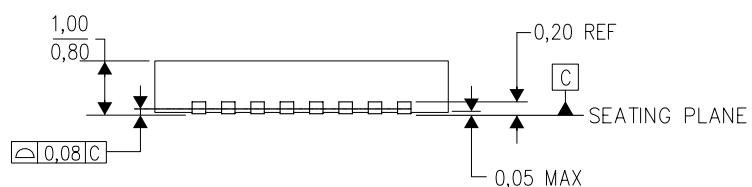

RHB (S-PVQFN-N32)

PLASTIC QUAD FLATPACK NO-LEAD

Bottom View

4204326/D 06/11

NOTES:

- A. All linear dimensions are in millimeters. Dimensioning and tolerancing per ASME Y14.5M-1994.

- B. This drawing is subject to change without notice.

- C. QFN (Quad Flatpack No-Lead) Package configuration.

- D. The package thermal pad must be soldered to the board for thermal and mechanical performance.

- E. See the additional figure in the Product Data Sheet for details regarding the exposed thermal pad features and dimensions.

- F. Falls within JEDEC MO-220.

RHB (S-PVQFN-N32)

PLASTIC QUAD FLATPACK NO-LEAD

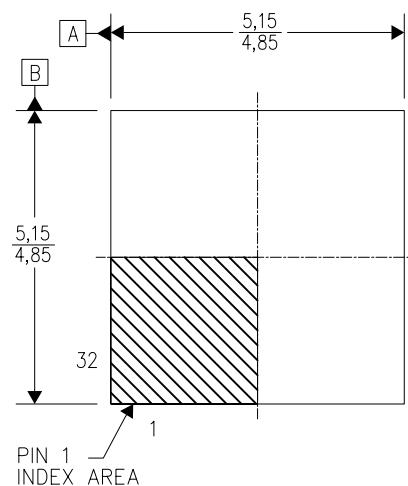

## THERMAL INFORMATION

This package incorporates an exposed thermal pad that is designed to be attached directly to an external heatsink. The thermal pad must be soldered directly to the printed circuit board (PCB). After soldering, the PCB can be used as a heatsink. In addition, through the use of thermal vias, the thermal pad can be attached directly to the appropriate copper plane shown in the electrical schematic for the device, or alternatively, can be attached to a special heatsink structure designed into the PCB. This design optimizes the heat transfer from the integrated circuit (IC).

For information on the Quad Flatpack No-Lead (QFN) package and its advantages, refer to Application Report, QFN/SON PCB Attachment, Texas Instruments Literature No. SLUA271. This document is available at [www.ti.com](http://www.ti.com).

The exposed thermal pad dimensions for this package are shown in the following illustration.

## PIN 1 INDICATOR

C 0,3

Bottom View

## Exposed Thermal Pad Dimensions

4206356-3/AC 05/15

NOTE: A. All linear dimensions are in millimeters

RHB (S-PVQFN-N32)

PLASTIC QUAD FLATPACK NO-LEAD

NOTES:

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. This package is designed to be soldered to a thermal pad on the board. Refer to Application Note, Quad Flat-Pack Packages, Texas Instruments Literature No. SLUA271, and also the Product Data Sheets for specific thermal information, via requirements, and recommended board layout. These documents are available at [www.ti.com](http://www.ti.com) <<http://www.ti.com>>.

- D. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Refer to IPC 7525 for stencil design considerations.

- E. Customers should contact their board fabrication site for recommended solder mask tolerances and via tenting recommendations for any larger diameter vias placed in the thermal pad.

## 重要声明

德州仪器 (TI) 公司有权按照最新发布的 JESD46 对其半导体产品和服务进行纠正、增强、改进和其他修改，并不再按最新发布的 JESD48 提供任何产品和服务。买方在下订单前应获取最新的相关信息，并验证这些信息是否完整且是最新的。

TI 公布的半导体产品销售条款 (<http://www.ti.com/sc/docs/stdterms.htm>) 适用于 TI 已认证和批准上市的已封装集成电路产品的销售。另有其他条款可能适用于其他类型 TI 产品及服务的使用或销售。

复制 TI 数据表上 TI 信息的重要部分时，不得变更该等信息，且必须随附所有相关保证、条件、限制和通知，否则不得复制。TI 对该等复制文件不承担任何责任。第三方信息可能受到其它限制条件的制约。在转售 TI 产品或服务时，如果存在对产品或服务参数的虚假陈述，则会失去相关 TI 产品或服务的明示或暗示保证，且构成不公平的、欺诈性商业行为。TI 对此类虚假陈述不承担任何责任。

买方和在系统中整合 TI 产品的其他开发人员（总称“设计人员”）理解并同意，设计人员在设计应用时应自行实施独立的分析、评价和判断，且应全权负责并确保应用的安全性，及设计人员的应用（包括应用中使用的所有 TI 产品）应符合所有适用的法律法规及其他相关要求。设计人员就自己设计的应用声明，其具备制订和实施下列保障措施所需的一切必要专业知识，能够（1）预见故障的危险后果，（2）监视故障及其后果，以及（3）降低可能导致危险的故障几率并采取适当措施。设计人员同意，在使用或分发包含 TI 产品的任何应用前，将彻底测试该等应用和该等应用中所用 TI 产品的功能。

TI 提供技术、应用或其他设计建议、质量特点、可靠性数据或其他服务或信息，包括但不限于与评估模块有关的参考设计和材料（总称“TI 资源”），旨在帮助设计人员开发整合了 TI 产品的应用，如果设计人员（个人，或如果是代表公司，则为设计人员的公司）以任何方式下载、访问或使用任何特定的 TI 资源，即表示其同意仅为该等目标，按照本通知的条款使用任何特定 TI 资源。

TI 所提供的 TI 资源，并未扩大或以其他方式修改 TI 对 TI 产品的公开适用的质保及质保免责声明；也未导致 TI 承担任何额外的义务或责任。TI 有权对 TI 资源进行纠正、增强、改进和其他修改。除特定 TI 资源的公开文档中明确列出的测试外，TI 未进行任何其他测试。

设计人员只有在开发包含该等 TI 资源所列 TI 产品的应用时，才被授权使用、复制和修改任何相关单项 TI 资源。但并未依据禁止反言原则或其他法理授予您任何 TI 知识产权的任何其他明示或默示的许可，也未授予您 TI 或第三方的任何技术或知识产权的许可，该等产权包括但不限于任何专利权、版权、屏蔽作品权或与使用 TI 产品或服务的任何整合、机器制作、流程相关的其他知识产权。涉及或参考了第三方产品或服务的信息不构成使用此类产品或服务的许可或与其相关的保证或认可。使用 TI 资源可能需要您向第三方获得对该等第三方专利或其他知识产权的许可。

TI 资源系“按原样”提供。TI 兹免除对资源及其使用作出所有其他明确或默认的保证或陈述，包括但不限于对准确性或完整性、产权保证、无屡发故障保证，以及适销性、适合特定用途和不侵犯任何第三方知识产权的任何默认保证。TI 不负责任任何申索，包括但不限于因组合产品所致或与之有关的申索，也不为或对设计人员进行辩护或赔偿，即使该等产品组合已列于 TI 资源或其他地方。对因 TI 资源或其使用引起或与之有关的任何实际的、直接的、特殊的、附带的、间接的、惩罚性的、偶发的、从属或惩戒性损害赔偿，不管 TI 是否获悉可能会产生上述损害赔偿，TI概不负责。

除 TI 已明确指出特定产品已达到特定行业标准（例如 ISO/TS 16949 和 ISO 26262）的要求外，TI 不对未达到任何该等行业标准要求而承担任何责任。

如果 TI 明确宣称产品有助于功能安全或符合行业功能安全标准，则该等产品旨在帮助客户设计和创作自己的符合相关功能安全标准和要求的应用。在应用内使用产品的行为本身不会配有任何安全特性。设计人员必须确保遵守适用于其应用的相关安全要求和标准。设计人员不可将任何 TI 产品用于关乎性命的医疗设备，除非已由各方获得授权的管理人员签署专门的合同对此类应用专门作出规定。关乎性命的医疗设备是指出现故障会导致严重身体伤害或死亡的医疗设备（例如生命保障设备、心脏起搏器、心脏除颤器、人工心脏泵、神经刺激器以及植入设备）。此类设备包括但不限于，美国食品药品监督管理局认定为 III 类设备的设备，以及在美国以外的其他国家或地区认定为同等类别设备的所有医疗设备。

TI 可能明确指定某些产品具备某些特定资格（例如 Q100、军用级或增强型产品）。设计人员同意，其具备一切必要专业知识，可以为自己的应用选择适合的产品，并且正确选择产品的风险由设计人员承担。设计人员单方面负责遵守与该等选择有关的所有法律或监管要求。

设计人员同意向 TI 及其代表全额赔偿因其不遵守本通知条款和条件而引起的任何损害、费用、损失和/或责任。

邮寄地址：上海市浦东新区世纪大道 1568 号中建大厦 32 楼，邮政编码：200122

Copyright © 2017 德州仪器半导体技术（上海）有限公司