# THS4532 超低功耗、轨到轨输出、全差分放大器

## 1 特性

- 超低功耗:

- 电压: 2.5V 至 5.5V

- 电流: 250 $\mu$ A

- 省电模式: 0.5 $\mu$ A (典型值)

- 全差分架构

- 带宽: 36MHz

- 转换速率: 200V/ $\mu$ s

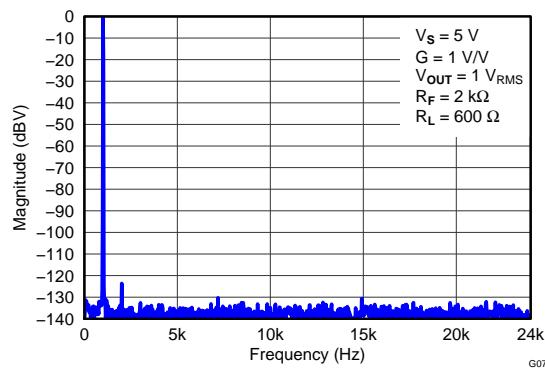

- 总谐波失真 (THD): 1kHz (1V<sub>RMS</sub>,  $R_L$ =2k $\Omega$ ) 时为 -120dBc

- 输入电压噪声: 10nV/ $\sqrt{\text{Hz}}$ (f=1kHz)

- 高 DC 精度:

- $V_{OS}$ :  $\pm 100\mu$ V

- $V_{OS}$ 漂移:  $\pm 3\mu$ V/ $^{\circ}$ C (-40 $^{\circ}$ C 至 +125 $^{\circ}$ C)

- $A_{OL}$ : 114dB

- 轨到轨输出 (RRO)

- 负电源轨输入 (NRI)

- 输出共模控制

## 2 应用

- 低功耗逐次逼近 (SAR), 三角积分模数转换器 (ADC) 驱动器

- 低功耗、高性能:

- 差分到差分放大器

- 单端到差分放大器

- 低功耗、宽带宽差分驱动器

- 低功耗、宽带宽差分信号调节

- 高通道数和高功率密度系统

## 3 说明

THS4532 是一款低功耗、全差分放大器, 其具有低于负电源轨的输入共模范围以及轨到轨输出。此器件设计用于能耗和功率耗散都十分关键的低功率数据采集系统和高密度应用。

此器件特有精确输出共模控制, 此控制可实现驱动模数转换器 (ADC) 时的 dc 耦合。与低于负电源轨和轨到轨输出的输入共模范围相耦合, 此控制可只使用 2.5V 至 5V 的单电源轻松实现单端接地基准信号源与逐次逼近 (SAR) 的连接和三角积分( $\Delta\Sigma$ ) ADC 的对接。

THS4532 也是一款适用于通用、低功耗差分信号调节应用的实用工具。

该器件在 -40 $^{\circ}$ C 至 125 $^{\circ}$ C 的扩展级工业温度范围内额定运行。该器件提供以下封装选项:

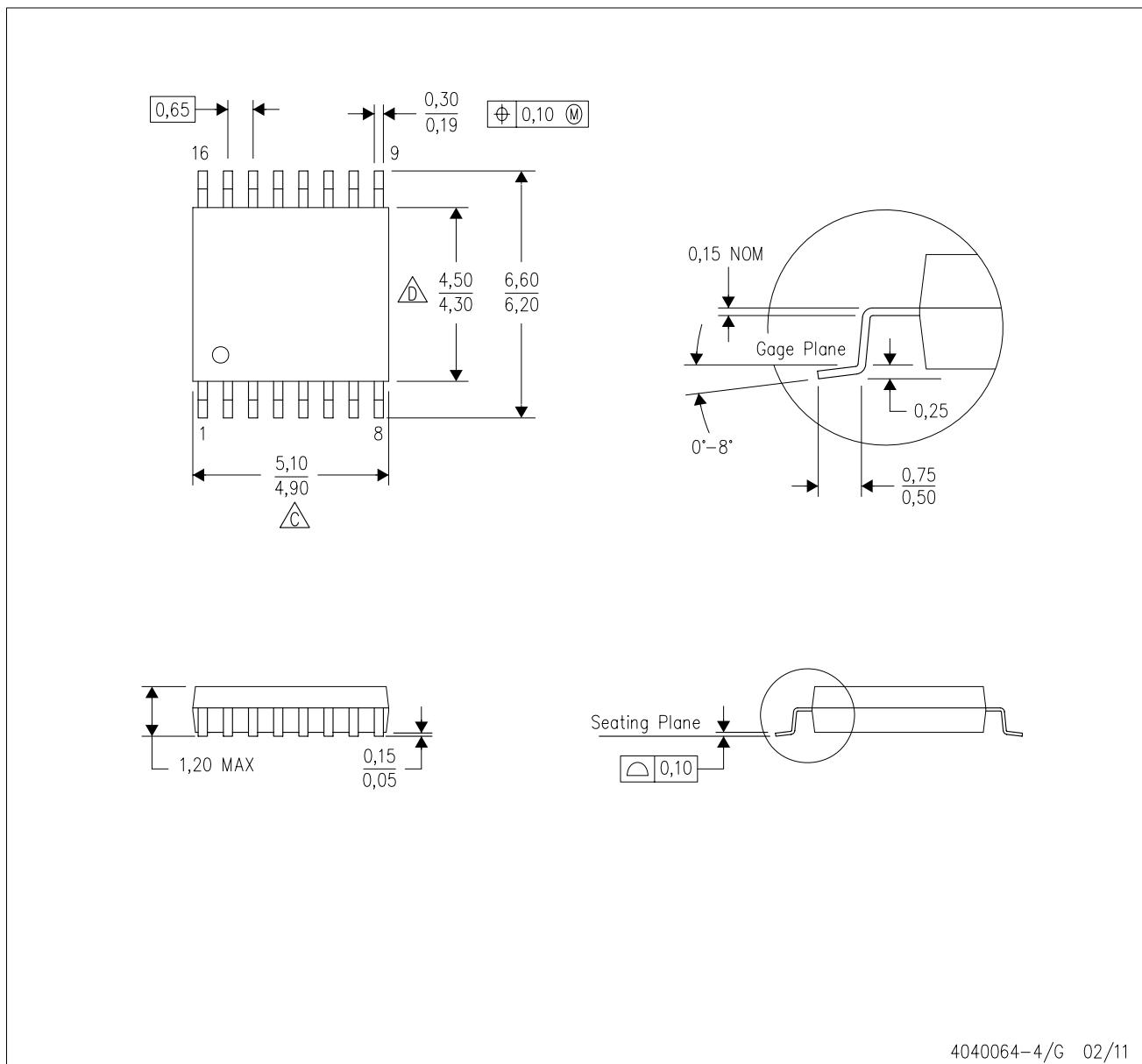

### 器件信息<sup>(1)</sup>

| 器件型号    | 封装    | 封装尺寸 (标称值)      |

|---------|-------|-----------------|

| THS4532 | TSSOP | 5.00mm x 4.40mm |

(1) 如需了解所有可用封装, 请见数据表末尾的可订购产品附录。

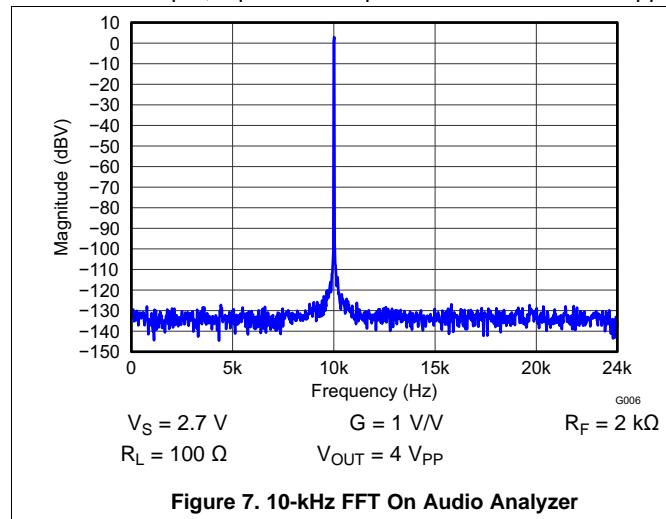

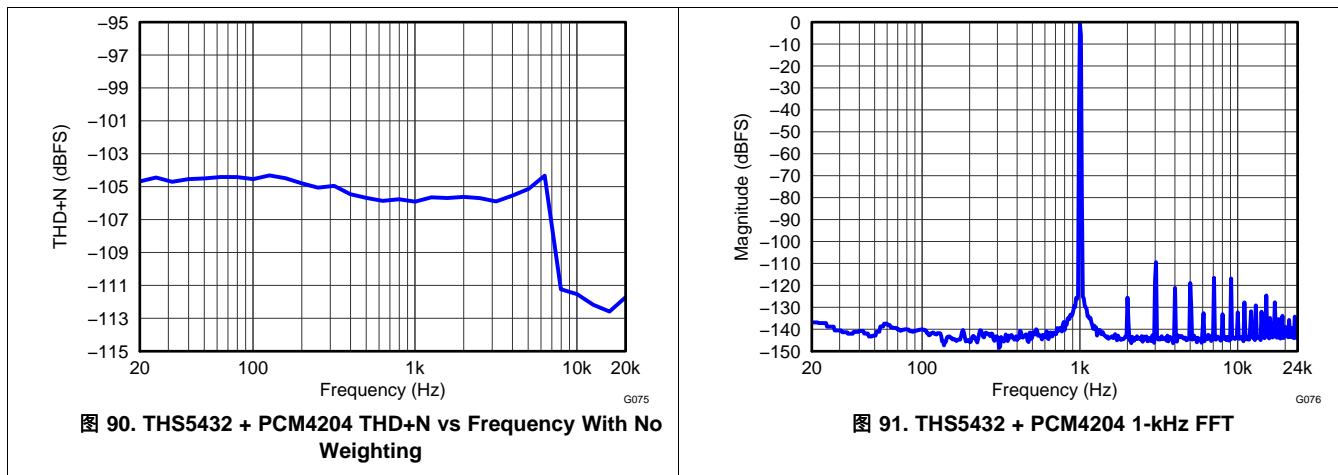

音频分析仪中的 1kHz 快速傅里叶变换 (FFT) 图

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications, intellectual property matters and other important disclaimers. PRODUCTION DATA.

English Data Sheet: SLOS829

## 目录

|          |                                                  |           |           |                                       |           |

|----------|--------------------------------------------------|-----------|-----------|---------------------------------------|-----------|

| <b>1</b> | <b>特性</b>                                        | <b>1</b>  | 8.3       | Feature Description                   | 25        |

| <b>2</b> | <b>应用</b>                                        | <b>1</b>  | 8.4       | Device Functional Modes               | 28        |

| <b>3</b> | <b>说明</b>                                        | <b>1</b>  | <b>9</b>  | <b>Application and Implementation</b> | <b>29</b> |

| <b>4</b> | <b>修订历史记录</b>                                    | <b>2</b>  | 9.1       | Application Information               | 29        |

| <b>5</b> | <b>Related Products</b>                          | <b>3</b>  | 9.2       | Typical Applications                  | 37        |

| <b>6</b> | <b>Pin Configuration and Functions</b>           | <b>4</b>  | 9.3       | Systems Examples                      | 41        |

| <b>7</b> | <b>Specifications</b>                            | <b>5</b>  | <b>10</b> | <b>Power Supply Recommendations</b>   | <b>47</b> |

| 7.1      | Absolute Maximum Ratings                         | 5         | <b>11</b> | <b>Layout</b>                         | <b>48</b> |

| 7.2      | ESD Ratings                                      | 5         | 11.1      | Layout Guidelines                     | 48        |

| 7.3      | Recommended Operating Conditions                 | 5         | 11.2      | Layout Example                        | 49        |

| 7.4      | Thermal Information                              | 5         | <b>12</b> | <b>器件和文档支持</b>                        | <b>53</b> |

| 7.5      | Electrical Characteristics: $V_S = 2.7\text{ V}$ | 6         | 12.1      | 文档支持                                  | 53        |

| 7.6      | Electrical Characteristics: $V_S = 5\text{ V}$   | 9         | 12.2      | 社区资源                                  | 53        |

| 7.7      | Typical Characteristics                          | 12        | 12.3      | 商标                                    | 53        |

| <b>8</b> | <b>Detailed Description</b>                      | <b>25</b> | 12.4      | 静电放电警告                                | 53        |

| 8.1      | Overview                                         | 25        | 12.5      | Glossary                              | 53        |

| 8.2      | Functional Block Diagram                         | 25        | <b>13</b> | 机械、封装和可订购信息                           | 53        |

**4 修订历史记录**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| Changes from Original (February 2013) to Revision A                                                                                                  | Page |

|------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| • 已添加 <i>ESD</i> 额定值表, 建议运行条件, 详细说明部分, 特性描述部分, 器件功能模式部分以及应用和实施部分。电源相关建议部分, 布局部分, 器件和文档支持部分以及机械、封装和可订购信息部分                                            | 1    |

| • Changed $V_{OCM} = \text{open To: } V_{OCM} = +V_S/2$ in the test conditions of <i>Electrical Characteristics: <math>V_S = 2.7\text{ V}</math></i> | 6    |

| • Added Note 3 to the <i>Electrical Characteristics: <math>V_S = 2.7\text{ V}</math></i> table.                                                      | 7    |

| • Changed $V_{OCM} = \text{open To: } V_{OCM} = +V_S/2$ in the test conditions of <i>Electrical Characteristics: <math>V_S = 5\text{ V}</math></i>   | 9    |

| • Changed <i>Typical Characteristics: <math>V_S = 2.7\text{ V}</math></i> Conditions deleted text "Channel 1"                                        | 13   |

| • Changed <i>Typical Characteristics: <math>V_S = 5\text{ V}</math></i> Conditions deleted text "Channel 1"                                          | 19   |

## 5 Related Products

**Table 1. Related Amplifiers**

| DEVICE  | BW (MHz) | I <sub>Q</sub> (mA) | THD (dBc) at 100 kHz | V <sub>N</sub> (nV/√Hz) | RAIL-TO-RAIL     | DUAL PART NUMBERS       |

|---------|----------|---------------------|----------------------|-------------------------|------------------|-------------------------|

| THS4531 | 36       | 0.25                | -104                 | 10                      | Negative In, Out | <a href="#">THS4532</a> |

| THS4121 | 100      | 16                  | -79                  | 5.4                     | Out              |                         |

| THS4521 | 145      | 1.14                | -120                 | 4.6                     | Negative In, Out | <a href="#">THS4522</a> |

| THS4131 | 150      | 16                  | -107                 | 1.3                     | No               |                         |

| THS4520 | 620      | 14.2                | -107                 | 2                       | Out              |                         |

| THS4541 | 850      | 10.1                | -137                 | 2.2                     | Negative In, Out |                         |

**Table 2. Related Precision ADCs**

| DEVICE   | BITS | MAX DATA RATE (kSPS) | NOMINAL SUPPLY (V) | NOMINAL I <sub>CC</sub> (mA)<br>MAX CLK RATE | TYPICAL POWER (mW)<br>MAX CLK RATE |

|----------|------|----------------------|--------------------|----------------------------------------------|------------------------------------|

| ADS8881  | 18   | 1000                 | 5                  | 1.1                                          | 5.5                                |

| ADS8861  | 16   | 1000                 | 3.3                | 1.67                                         | 5.3                                |

| ADS8321E | 16   | 100                  | 5                  | 0.9                                          | 4.5                                |

| ADS7945  | 14   | 2000                 | 5                  | 2.32                                         | 5.8/ch (dual)                      |

| ADS7044  | 12   | 1000                 | 3                  | 0.3                                          | 0.9                                |

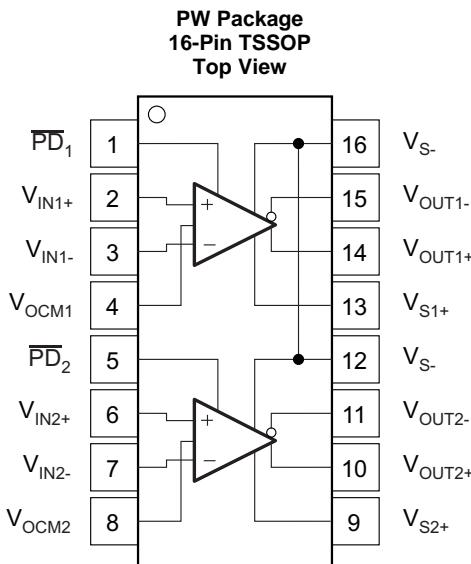

## 6 Pin Configuration and Functions

### Pin Functions

| PIN                |        | I/O | DESCRIPTION                                                                                                                                          |

|--------------------|--------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME               | NO.    |     |                                                                                                                                                      |

| PD <sub>1</sub>    | 1      | —   | Power-down 1, $\overline{PD}$ = logic low = low power mode, $\overline{PD}$ = logic high = normal operation<br><b>(PIN MUST BE DRIVEN)</b>           |

| PD <sub>2</sub>    | 5      | —   | Amplifier 2 Power-down, $\overline{PD}$ = logic low = low power mode, $\overline{PD}$ = logic high = normal operation<br><b>(PIN MUST BE DRIVEN)</b> |

| V <sub>IN1+</sub>  | 2      | I   | Noninverting amplifier 1 input                                                                                                                       |

| V <sub>IN1-</sub>  | 3      | I   | Inverting amplifier 1 input                                                                                                                          |

| V <sub>IN2+</sub>  | 6      | I   | Noninverting amplifier 2 input                                                                                                                       |

| V <sub>IN2-</sub>  | 7      | I   | Inverting amplifier 2 input                                                                                                                          |

| V <sub>OCM1</sub>  | 4      | I   | Common-mode voltage input 1                                                                                                                          |

| V <sub>OCM2</sub>  | 8      | I   | Common-mode voltage input 2                                                                                                                          |

| V <sub>OUT1+</sub> | 14     | O   | Noninverting amplifier 1 output                                                                                                                      |

| V <sub>OUT1-</sub> | 15     | O   | Inverting amplifier 1 output                                                                                                                         |

| V <sub>OUT2+</sub> | 10     | O   | Noninverting amplifier 2 output                                                                                                                      |

| V <sub>OUT2-</sub> | 11     | O   | Inverting amplifier 2 output                                                                                                                         |

| V <sub>S-</sub>    | 12, 16 | I   | Negative power-supply input. Note V <sub>S</sub> tied together on multichannel devices                                                               |

| V <sub>S1+</sub>   | 13     | I   | Amplifier 1 positive power-supply input                                                                                                              |

| V <sub>S2+</sub>   | 9      | I   | Amplifier 2 positive power-supply input                                                                                                              |

## 7 Specifications

### 7.1 Absolute Maximum Ratings<sup>(1)</sup>

|                                                                       | MIN                            | MAX              | UNIT |

|-----------------------------------------------------------------------|--------------------------------|------------------|------|

| Supply voltage, $V_{S-}$ to $V_{S+}$                                  |                                | 5.5              | V    |

| Input/output voltage, $V_{IN\pm}$ , $V_{OUT\pm}$ , and $V_{OCM}$ pins | $(V_{S-}) - 0.7$               | $(V_{S+}) + 0.7$ | V    |

| Differential input voltage, $V_{ID}$                                  |                                | 1                | V    |

| Continuous output current, $I_O$                                      |                                | 50               | mA   |

| Continuous input current, $I_i$                                       |                                | 0.75             | mA   |

| Continuous power dissipation                                          | See <i>Thermal Information</i> |                  |      |

| Maximum junction temperature, $T_J$                                   |                                | 150              | °C   |

| Operating junction temperature, $T_J$                                 | -40                            | 125              | °C   |

| Storage temperature, $T_{stg}$                                        | -65                            | 150              | °C   |

(1) Stresses beyond those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under *Recommended Operating Conditions*. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### 7.2 ESD Ratings

|             |                                                                                | VALUE      | UNIT |

|-------------|--------------------------------------------------------------------------------|------------|------|

| $V_{(ESD)}$ | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | $\pm 2500$ | V    |

|             | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | $\pm 500$  |      |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|          | MIN                   | NOM | MAX | UNIT |

|----------|-----------------------|-----|-----|------|

| $V_{S+}$ | Single-supply voltage | 2.7 | 5   | 5.4  |

| $T_A$    | Ambient temperature   | -40 | 25  | 125  |

### 7.4 Thermal Information

| THERMAL METRIC <sup>(1)</sup> |                                              | THS4532    | UNIT |

|-------------------------------|----------------------------------------------|------------|------|

|                               |                                              | TSSOP (PW) |      |

|                               |                                              | 16 PINS    |      |

| $R_{\theta JA}$               | Junction-to-ambient thermal resistance       | 122.4      | °C/W |

| $R_{\theta JC(\text{top})}$   | Junction-to-case (top) thermal resistance    | 61.2       |      |

| $R_{\theta JB}$               | Junction-to-board thermal resistance         | 66.7       |      |

| $\Psi_{JT}$                   | Junction-to-top characterization parameter   | 14.4       |      |

| $\Psi_{JB}$                   | Junction-to-board characterization parameter | 66.2       |      |

| $R_{\theta JC(\text{bot})}$   | Junction-to-case (bottom) thermal resistance | N/A        |      |

(1) For more information about traditional and new thermal metrics, see the *Semiconductor and IC Package Thermal Metrics* application report, [SPRA953](#).

## 7.5 Electrical Characteristics: $V_S = 2.7$ V

Test conditions at  $T_A = 25^\circ\text{C}$ ,  $V_{S+} = 2.7$  V,  $V_{S-} = 0$  V,  $V_{OCM} = +V_S/2^{(1)}$ ,  $V_{OUT} = 2$  V<sub>PP</sub>,  $R_F = 2$  k $\Omega$ ,  $R_L = 2$  k $\Omega$  differential,  $G = 1$  V/V, single-ended input, differential output, and input and output referenced to mid-supply, unless otherwise noted.

| PARAMETER                            | TEST CONDITIONS                             | MIN     | TYP | MAX | UNIT                   | TEST LEVEL <sup>(2)</sup> |  |

|--------------------------------------|---------------------------------------------|---------|-----|-----|------------------------|---------------------------|--|

| <b>AC PERFORMANCE</b>                |                                             |         |     |     |                        |                           |  |

| Small-signal bandwidth               | $V_{OUT} = 100$ mV <sub>PP</sub> , $G = 1$  | 34      |     |     | MHz                    | C                         |  |

|                                      | $V_{OUT} = 100$ mV <sub>PP</sub> , $G = 2$  | 16      |     |     |                        |                           |  |

|                                      | $V_{OUT} = 100$ mV <sub>PP</sub> , $G = 5$  | 6       |     |     |                        |                           |  |

|                                      | $V_{OUT} = 100$ mV <sub>PP</sub> , $G = 10$ | 2.7     |     |     |                        |                           |  |

| Gain-bandwidth product               | $V_{OUT} = 100$ mV <sub>PP</sub> , $G = 10$ | 27      |     |     | MHz                    |                           |  |

| Large-signal bandwidth               | $V_{OUT} = 2$ V <sub>PP</sub> , $G = 1$     | 34      |     |     | MHz                    |                           |  |

| Bandwidth for 0.1-dB flatness        | $V_{OUT} = 2$ V <sub>PP</sub> , $G = 1$     | 12      |     |     | MHz                    |                           |  |

| Slew rate, rise/fall, 25% to 75%     |                                             | 190/320 |     |     | V/ $\mu$ s             |                           |  |

| Rise/fall time, 10% to 90%           |                                             | 5.2/6.1 |     |     | ns                     |                           |  |

| Settling time to 1%, rise/fall       | $V_{OUT} = 2$ -V step                       | 25/20   |     |     | ns                     | C                         |  |

| Settling time to 0.1%, rise/fall     |                                             | 60/60   |     |     |                        |                           |  |

| Settling time to 0.01%, rise/fall    |                                             | 150/110 |     |     |                        |                           |  |

| Overshoot/undershoot, rise/fall      |                                             | 1/1%    |     |     |                        |                           |  |

| 2nd-order harmonic distortion        | $f = 1$ kHz, $V_{OUT} = 1$ V <sub>RMS</sub> | -122    |     |     | dBc                    |                           |  |

|                                      | $f = 10$ kHz                                | -127    |     |     |                        |                           |  |

|                                      | $f = 1$ MHz                                 | -59     |     |     |                        |                           |  |

| 3rd-order harmonic distortion        | $f = 1$ kHz, $V_{OUT} = 1$ V <sub>RMS</sub> | -130    |     |     | dBc                    | C                         |  |

|                                      | $f = 10$ kHz                                | -135    |     |     |                        |                           |  |

|                                      | $f = 1$ MHz                                 | -70     |     |     |                        |                           |  |

| 2nd-order intermodulation distortion | $f = 1$ MHz, 200-kHz tone spacing,          | -83     |     |     | dBc                    | C                         |  |

| 3rd-order intermodulation distortion | $V_{OUT}$ envelope = 2 V <sub>PP</sub>      | -81     |     |     |                        |                           |  |

| Input voltage noise                  | $f = 1$ kHz                                 | 10      |     |     | nV/ $\sqrt{\text{Hz}}$ |                           |  |

| Voltage noise 1/f corner frequency   |                                             | 45      |     |     | Hz                     |                           |  |

| Input current noise                  | $f = 100$ kHz                               | 0.25    |     |     | pA/ $\sqrt{\text{Hz}}$ |                           |  |

| Current noise 1/f corner frequency   |                                             | 6.5     |     |     | kHz                    |                           |  |

| Overdrive recovery time              | Overdrive = 0.5 V                           | 65      |     |     | ns                     |                           |  |

| Output balance error                 | $V_{OUT} = 100$ mV, $f = 1$ MHz             | -65     |     |     | dB                     |                           |  |

| Closed-loop output impedance         | $f = 1$ MHz (differential)                  | 2.5     |     |     | $\Omega$               |                           |  |

| Channel-to-channel crosstalk         | $f = 10$ kHz, measured differentially       | -133    |     |     | dB                     |                           |  |

(1) Node set to midsupply externally; 0.1  $\mu$ F

(2) Test levels (all values set by characterization and simulation): (A) 100% tested at  $+25^\circ\text{C}$ ; over temperature limits by characterization and simulation. (B) Not tested in production; limits set by characterization and simulation. (C) Typical value only for information.

## Electrical Characteristics: $V_S = 2.7$ V (continued)

Test conditions at  $T_A = 25^\circ\text{C}$ ,  $V_{S+} = 2.7$  V,  $V_{S-} = 0$  V,  $V_{OCM} = +V_S/2^{(1)}$ ,  $V_{OUT} = 2$  V<sub>PP</sub>,  $R_F = 2$  k $\Omega$ ,  $R_L = 2$  k $\Omega$  differential,  $G = 1$  V/V, single-ended input, differential output, and input and output referenced to mid-supply, unless otherwise noted.

| PARAMETER                                 | TEST CONDITIONS                                                 | MIN             | TYP             | MAX        | UNIT                                 | TEST LEVEL (2) |

|-------------------------------------------|-----------------------------------------------------------------|-----------------|-----------------|------------|--------------------------------------|----------------|

| <b>DC PERFORMANCE</b>                     |                                                                 |                 |                 |            |                                      |                |

| Open-loop voltage gain ( $A_{OL}$ )       |                                                                 | 100             | 113             |            | dB                                   | A              |

| Input-referred offset voltage             | $T_A = 25^\circ\text{C}$                                        |                 | $\pm 80$        | $\pm 400$  | $\mu\text{V}$                        | A              |

|                                           | $T_A = 0^\circ\text{C}$ to $70^\circ\text{C}$                   |                 |                 | $\pm 715$  |                                      |                |

|                                           | $T_A = -40^\circ\text{C}$ to $85^\circ\text{C}$                 |                 |                 | $\pm 855$  |                                      | B              |

|                                           | $T_A = -40^\circ\text{C}$ to $125^\circ\text{C}$                |                 |                 | $\pm 1300$ |                                      |                |

| Input offset voltage drift <sup>(3)</sup> | $T_A = 0^\circ\text{C}$ to $70^\circ\text{C}$                   |                 | $\pm 2$         | $\pm 7$    | $\mu\text{V}/^\circ\text{C}$         | B              |

|                                           | $T_A = -40^\circ\text{C}$ to $85^\circ\text{C}$                 |                 | $\pm 2$         | $\pm 7$    |                                      |                |

|                                           | $T_A = -40^\circ\text{C}$ to $125^\circ\text{C}$                |                 | $\pm 3$         | $\pm 9$    |                                      |                |

| Input bias current                        | $T_A = 25^\circ\text{C}$                                        | 200             | 250             |            | $\text{nA}$                          | A              |

|                                           | $T_A = 0^\circ\text{C}$ to $70^\circ\text{C}$                   |                 | 275             |            |                                      |                |

|                                           | $T_A = -40^\circ\text{C}$ to $85^\circ\text{C}$                 |                 | 286             |            |                                      | B              |

|                                           | $T_A = -40^\circ\text{C}$ to $125^\circ\text{C}$                |                 | 305             |            |                                      |                |

| Input bias current drift <sup>(3)</sup>   | $T_A = 0^\circ\text{C}$ to $70^\circ\text{C}$                   | 0.45            | 0.55            |            | $\text{nA}/^\circ\text{C}$           | B              |

|                                           | $T_A = -40^\circ\text{C}$ to $85^\circ\text{C}$                 | 0.45            | 0.55            |            |                                      |                |

|                                           | $T_A = -40^\circ\text{C}$ to $125^\circ\text{C}$                | 0.45            | 0.55            |            |                                      |                |

| Input offset current                      | $T_A = 25^\circ\text{C}$                                        | $\pm 5$         | $\pm 50$        |            | $\text{nA}$                          | A              |

|                                           | $T_A = 0^\circ\text{C}$ to $70^\circ\text{C}$                   |                 | $\pm 55$        |            |                                      |                |

|                                           | $T_A = -40^\circ\text{C}$ to $85^\circ\text{C}$                 |                 | $\pm 57$        |            |                                      | B              |

|                                           | $T_A = -40^\circ\text{C}$ to $125^\circ\text{C}$                |                 | $\pm 60$        |            |                                      |                |

| Input offset current drift <sup>(3)</sup> | $T_A = 0^\circ\text{C}$ to $70^\circ\text{C}$                   | $\pm 0.03$      | $\pm 0.1$       |            | $\text{nA}/^\circ\text{C}$           | B              |

|                                           | $T_A = -40^\circ\text{C}$ to $85^\circ\text{C}$                 | $\pm 0.03$      | $\pm 0.1$       |            |                                      |                |

|                                           | $T_A = -40^\circ\text{C}$ to $125^\circ\text{C}$                | $\pm 0.03$      | $\pm 0.1$       |            |                                      |                |

| <b>INPUT</b>                              |                                                                 |                 |                 |            |                                      |                |

| Common-mode input low                     | $T_A = 25^\circ\text{C}$ , CMRR > 87 dB                         | $V_{S-} - 0.2$  | $V_{S-}$        |            | V                                    | A              |

|                                           | $T_A = -40^\circ\text{C}$ to $125^\circ\text{C}$ , CMRR > 87 dB | $V_{S-} - 0.2$  | $V_{S-}$        |            |                                      | B              |

| Common-mode input high                    | $T_A = 25^\circ\text{C}$ , CMRR > 87 dB                         | $V_{S+} - 1.2$  | $V_{S+} - 1.1$  |            | V                                    | A              |

|                                           | $T_A = -40^\circ\text{C}$ to $125^\circ\text{C}$ , CMRR > 87 dB | $V_{S+} - 1.2$  | $V_{S+} - 1.1$  |            |                                      | B              |

| Common-mode rejection ratio               |                                                                 | 90              | 116             |            | dB                                   | A              |

| Input impedance common-mode               |                                                                 | 200             | $\parallel 1.2$ |            | $\text{k}\Omega \parallel \text{pF}$ | C              |

| Input impedance differential mode         |                                                                 | 200             | $\parallel 1$   |            |                                      | C              |

| <b>OUTPUT</b>                             |                                                                 |                 |                 |            |                                      |                |

| Single-ended output voltage: low          | $T_A = 25^\circ\text{C}$                                        | $V_{S+} + 0.06$ | $V_{S-} + 0.2$  |            | V                                    | A              |

|                                           | $T_A = -40^\circ\text{C}$ to $125^\circ\text{C}$                | $V_{S+} + 0.06$ | $V_{S-} + 0.2$  |            |                                      | B              |

| Single-ended output voltage: high         | $T_A = 25^\circ\text{C}$                                        | $V_{S+} - 0.2$  | $V_{S+} - 0.11$ |            | V                                    | A              |

|                                           | $T_A = -40^\circ\text{C}$ to $125^\circ\text{C}$                | $V_{S+} - 0.2$  | $V_{S+} - 0.11$ |            |                                      | B              |

| Output saturation voltage: high/low       |                                                                 | 110/60          |                 |            | mV                                   | C              |

| Linear output current drive               | $T_A = 25^\circ\text{C}$                                        | $\pm 15$        | $\pm 22$        |            | mA                                   | A              |

|                                           | $T_A = -40^\circ\text{C}$ to $125^\circ\text{C}$                | $\pm 15$        |                 |            |                                      | B              |

(3) Input offset voltage drift, input bias current drift, and input offset current drift are average values calculated by taking data at the end points, computing the difference, and dividing by the temperature range.

## Electrical Characteristics: $V_S = 2.7$ V (continued)

Test conditions at  $T_A = 25^\circ\text{C}$ ,  $V_{S+} = 2.7$  V,  $V_{S-} = 0$  V,  $V_{OCM} = +V_S/2^{(1)}$ ,  $V_{OUT} = 2$  V<sub>PP</sub>,  $R_F = 2$  k $\Omega$ ,  $R_L = 2$  k $\Omega$  differential,  $G = 1$  V/V, single-ended input, differential output, and input and output referenced to mid-supply, unless otherwise noted.

| PARAMETER                                                        | TEST CONDITIONS                                                                             | MIN        | TYP         | MAX       | UNIT             | TEST LEVEL (2) |

|------------------------------------------------------------------|---------------------------------------------------------------------------------------------|------------|-------------|-----------|------------------|----------------|

| <b>POWER SUPPLY</b>                                              |                                                                                             |            |             |           |                  |                |

| Specified operating voltage                                      |                                                                                             | 2.5        |             | 5.5       | V                | B              |

| Quiescent operating current/ch                                   | $T_A = 25^\circ\text{C}$ , $\overline{PD} = V_{S+}$                                         |            | 230         | 330       | $\mu\text{A}$    | A              |

|                                                                  | $T_A = -40^\circ\text{C}$ to $125^\circ\text{C}$ , $\overline{PD} = V_{S+}$                 |            | 270         | 370       |                  | B              |

| Power-supply rejection (PSRR)                                    |                                                                                             | 87         | 108         |           | dB               | A              |

| <b>POWER DOWN</b>                                                |                                                                                             |            |             |           |                  |                |

| Enable voltage threshold                                         | Specified on above 2.1 V                                                                    |            | 2.1         |           | V                | A              |

| Disable voltage threshold                                        | Specified off below 0.7 V                                                                   | 0.7        |             |           | V                | A              |

| Disable pin bias current                                         | $\overline{PD} = V_{S-} + 0.5$ V                                                            |            | 50          | 500       | nA               | A              |

| Power-down quiescent current                                     | $\overline{PD} = V_{S-} + 0.5$ V                                                            |            | 0.5         | 2         | $\mu\text{A}$    | A              |

| Turn-on time delay                                               | Time from $\overline{PD}$ = high to $V_{OUT} = 90\%$ of final value, $R_L = 200$ $\Omega$   |            | 650         |           | ns               | C              |

| Turn-off time delay                                              | Time from $\overline{PD}$ = low to $V_{OUT} = 10\%$ of original value, $R_L = 200$ $\Omega$ |            | 20          |           | ns               | C              |

| <b>OUTPUT COMMON-MODE VOLTAGE CONTROL (<math>V_{OCM}</math>)</b> |                                                                                             |            |             |           |                  |                |

| Small-signal bandwidth                                           | $V_{OCM}$ input = 100 mV <sub>PP</sub>                                                      |            | 23          |           | MHz              | C              |

| Slew rate                                                        | $V_{OCM}$ input = 1 V <sub>STEP</sub>                                                       |            | 14          |           | V/ $\mu\text{s}$ | C              |

| Gain                                                             |                                                                                             | 0.99       | 0.996       | 1.01      | V/V              | A              |

| Common-mode offset voltage                                       | Offset = output common-mode voltage – $V_{OCM}$ input voltage                               |            | $\pm 1$     | $\pm 5$   | mV               | A              |

| $V_{OCM}$ input bias current                                     | $V_{OCM} = (V_{S+} - V_{S-})/2$                                                             |            | $\pm 20$    | $\pm 100$ | nA               | A              |

| $V_{OCM}$ input voltage range                                    |                                                                                             | 0.8        | 0.75 to 1.9 | 1.75      | V                | A              |

| $V_{OCM}$ input impedance                                        |                                                                                             | 100    1.6 |             |           | k $\Omega$    pF | C              |

| Default voltage offset from $(V_{S+} - V_{S-})/2$                | Offset = output common-mode voltage – $(V_{S+} - V_{S-})/2$                                 |            | $\pm 3$     | $\pm 10$  | mV               | A              |

## 7.6 Electrical Characteristics: $V_S = 5$ V

Test conditions at  $T_A = +25^\circ\text{C}$ ,  $V_{S+} = 5$  V,  $V_{S-} = 0$  V,  $V_{OCM} = \text{open}$ ,  $V_{OUT} = 2$  V<sub>PP</sub>,  $R_F = 2$  k $\Omega$ ,  $R_L = 2$  k $\Omega$  differential,  $G = 1$  V/V, single-ended input, differential output, and input and output referenced to mid-supply, unless otherwise noted.

| PARAMETER                            | TEST CONDITIONS                                                              | MIN     | TYP | MAX | UNIT                   | TEST LEVEL <sup>(1)</sup> |

|--------------------------------------|------------------------------------------------------------------------------|---------|-----|-----|------------------------|---------------------------|

| <b>AC PERFORMANCE</b>                |                                                                              |         |     |     |                        |                           |

| Small-signal bandwidth               | $V_{OUT} = 100$ mV <sub>PP</sub> , $G = 1$                                   | 36      |     |     | MHz                    | C                         |

|                                      | $V_{OUT} = 100$ mV <sub>PP</sub> , $G = 2$                                   | 17      |     |     |                        |                           |

|                                      | $V_{OUT} = 100$ mV <sub>PP</sub> , $G = 5$                                   | 6       |     |     |                        |                           |

|                                      | $V_{OUT} = 100$ mV <sub>PP</sub> , $G = 10$                                  | 2.7     |     |     |                        |                           |

| Gain-bandwidth product               | $V_{OUT} = 100$ mV <sub>PP</sub> , $G = 10$                                  | 27      |     |     | MHz                    |                           |

| Large-signal bandwidth               | $V_{OUT} = 2$ V <sub>PP</sub> , $G = 1$                                      | 36      |     |     | MHz                    |                           |

| Bandwidth for 0.1-dB flatness        | $V_{OUT} = 2$ V <sub>PP</sub> , $G = 1$                                      | 15      |     |     | MHz                    |                           |

| Slew rate, rise/fall, 25% to 75%     |                                                                              | 220/390 |     |     | V/ $\mu$ s             |                           |

| Rise/fall time, 10% to 90%           |                                                                              | 4.6/5.6 |     |     | ns                     |                           |

| Settling time to 1%, rise/fall       | $V_{OUT} = 2$ V <sub>Step</sub>                                              | 25/20   |     |     | ns                     |                           |

| Settling time to 0.1%, rise/fall     |                                                                              | 60/60   |     |     | ns                     |                           |

| Settling time to 0.01%, rise/fall    |                                                                              | 150/110 |     |     | ns                     |                           |

| Overshoot/undershoot, rise/fall      |                                                                              | 1/1%    |     |     |                        |                           |

| 2nd-order harmonic distortion        | $f = 1$ kHz, $V_{OUT} = 1$ V <sub>RMS</sub>                                  | -122    |     |     | dBc                    | C                         |

|                                      | $f = 10$ kHz                                                                 | -128    |     |     |                        |                           |

|                                      | $f = 1$ MHz                                                                  | -60     |     |     |                        |                           |

| 3rd-order harmonic distortion        | $f = 1$ kHz, $V_{OUT} = 1$ V <sub>RMS</sub>                                  | -130    |     |     | dBc                    | C                         |

|                                      | $f = 10$ kHz                                                                 | -137    |     |     |                        |                           |

|                                      | $f = 1$ MHz                                                                  | -71     |     |     |                        |                           |

| 2nd-order intermodulation distortion | $f = 1$ MHz, 200-kHz tone spacing,<br>$V_{OUT}$ envelope = 2 V <sub>PP</sub> | -85     |     |     | dBc                    |                           |

| 3rd-order intermodulation distortion |                                                                              | -83     |     |     | dBc                    |                           |

| Input voltage noise                  | $f = 1$ kHz                                                                  | 10      |     |     | nV/ $\sqrt{\text{Hz}}$ |                           |

| Voltage noise 1/f corner frequency   |                                                                              | 45      |     |     | Hz                     |                           |

| Input current noise                  | $f = 100$ kHz                                                                | 0.25    |     |     | pA/ $\sqrt{\text{Hz}}$ |                           |

| Current noise 1/f corner frequency   |                                                                              | 6.5     |     |     | kHz                    |                           |

| Overdrive recovery time              | Overdrive = 0.5 V                                                            | 65      |     |     | ns                     |                           |

| Output balance error                 | $V_{OUT} = 100$ mV, $f = 1$ MHz                                              | -67     |     |     | dB                     |                           |

| Closed-loop output impedance         | $f = 1$ MHz (differential)                                                   | 2.5     |     |     | $\Omega$               |                           |

| Channel-to-channel crosstalk         | $f = 10$ kHz, measured differentially                                        | -133    |     |     | dB                     |                           |

(1) Test levels (all values set by characterization and simulation): (A) 100% tested at  $+25^\circ\text{C}$ ; over temperature limits by characterization and simulation. (B) Not tested in production; limits set by characterization and simulation. (C) Typical value only for information.

## Electrical Characteristics: $V_S = 5$ V (continued)

Test conditions at  $T_A = +25^\circ\text{C}$ ,  $V_{S+} = 5$  V,  $V_{S-} = 0$  V,  $V_{OCM} = \text{open}$ ,  $V_{OUT} = 2$  V<sub>PP</sub>,  $R_F = 2$  k $\Omega$ ,  $R_L = 2$  k $\Omega$  differential,  $G = 1$  V/V, single-ended input, differential output, and input and output referenced to mid-supply, unless otherwise noted.

| PARAMETER                                 | TEST CONDITIONS                                                 | MIN             | TYP             | MAX       | UNIT                                 | TEST LEVEL <sup>(1)</sup> |

|-------------------------------------------|-----------------------------------------------------------------|-----------------|-----------------|-----------|--------------------------------------|---------------------------|

| <b>DC PERFORMANCE</b>                     |                                                                 |                 |                 |           |                                      |                           |

| Open-loop voltage gain ( $A_{OL}$ )       |                                                                 | 100             | 114             |           | dB                                   | A                         |

| Input-referred offset voltage             | $T_A = 25^\circ\text{C}$                                        |                 | $\pm 80$        | $\pm 400$ | $\mu\text{V}$                        | A                         |

|                                           | $T_A = 0^\circ\text{C}$ to $70^\circ\text{C}$                   |                 | $\pm 715$       |           |                                      |                           |

|                                           | $T_A = -40^\circ\text{C}$ to $85^\circ\text{C}$                 |                 | $\pm 855$       |           |                                      | B                         |

|                                           | $T_A = -40^\circ\text{C}$ to $125^\circ\text{C}$                |                 | $\pm 1300$      |           |                                      |                           |

| Input offset voltage drift <sup>(2)</sup> | $T_A = 0^\circ\text{C}$ to $70^\circ\text{C}$                   |                 | $\pm 2$         | $\pm 7$   | $\mu\text{V}/^\circ\text{C}$         |                           |

|                                           | $T_A = -40^\circ\text{C}$ to $85^\circ\text{C}$                 |                 | $\pm 2$         | $\pm 7$   |                                      | B                         |

|                                           | $T_A = -40^\circ\text{C}$ to $125^\circ\text{C}$                |                 | $\pm 3$         | $\pm 9$   |                                      |                           |

| Input bias current                        | $T_A = 25^\circ\text{C}$                                        | 200             | 250             |           | $\text{nA}$                          | A                         |

|                                           | $T_A = 0^\circ\text{C}$ to $70^\circ\text{C}$                   |                 | 279             |           |                                      |                           |

|                                           | $T_A = -40^\circ\text{C}$ to $85^\circ\text{C}$                 |                 | 292             |           |                                      | B                         |

|                                           | $T_A = -40^\circ\text{C}$ to $125^\circ\text{C}$                |                 | 315             |           |                                      |                           |

| Input bias current drift <sup>(2)</sup>   | $T_A = 0^\circ\text{C}$ to $70^\circ\text{C}$                   | 0.5             | 0.65            |           | $\text{nA}/^\circ\text{C}$           |                           |

|                                           | $T_A = -40^\circ\text{C}$ to $85^\circ\text{C}$                 | 0.5             | 0.65            |           |                                      | B                         |

|                                           | $T_A = -40^\circ\text{C}$ to $125^\circ\text{C}$                | 0.5             | 0.65            |           |                                      |                           |

| Input offset current                      | $T_A = 25^\circ\text{C}$                                        | $\pm 5$         | $\pm 50$        |           | $\text{nA}$                          | A                         |

|                                           | $T_A = 0^\circ\text{C}$ to $70^\circ\text{C}$                   |                 | $\pm 55$        |           |                                      |                           |

|                                           | $T_A = -40^\circ\text{C}$ to $85^\circ\text{C}$                 |                 | $\pm 57$        |           |                                      | B                         |

|                                           | $T_A = -40^\circ\text{C}$ to $125^\circ\text{C}$                |                 | $\pm 60$        |           |                                      |                           |

| Input offset current drift <sup>(2)</sup> | $T_A = 0^\circ\text{C}$ to $70^\circ\text{C}$                   | $\pm 0.03$      | $\pm 0.1$       |           | $\text{nA}/^\circ\text{C}$           |                           |

|                                           | $T_A = -40^\circ\text{C}$ to $85^\circ\text{C}$                 | $\pm 0.03$      | $\pm 0.1$       |           |                                      | B                         |

|                                           | $T_A = -40^\circ\text{C}$ to $125^\circ\text{C}$                | $\pm 0.03$      | $\pm 0.1$       |           |                                      |                           |

| <b>INPUT</b>                              |                                                                 |                 |                 |           |                                      |                           |

| Common-mode input: low                    | $T_A = 25^\circ\text{C}$ , CMRR > 87 dB                         | $V_{S-} - 0.2$  | $V_{S-}$        |           | V                                    | A                         |

|                                           | $T_A = -40^\circ\text{C}$ to $125^\circ\text{C}$ , CMRR > 87 dB | $V_{S-} - 0.2$  | $V_{S-}$        |           |                                      | B                         |

| Common-mode input: high                   | $T_A = 25^\circ\text{C}$ , CMRR > 87 dB                         | $V_{S+} - 1.2$  | $V_{S+} - 1.1$  |           | V                                    | A                         |

|                                           | $T_A = -40^\circ\text{C}$ to $125^\circ\text{C}$ , CMRR > 87 dB | $V_{S+} - 1.2$  | $V_{S+} - 1.1$  |           |                                      | B                         |

| Common-mode rejection ratio               |                                                                 | 90              | 116             |           | dB                                   | A                         |

| Input impedance common-mode               |                                                                 | 200             | $\parallel 1.2$ |           | $\text{k}\Omega \parallel \text{pF}$ | C                         |

| Input impedance differential mode         |                                                                 | 200             | $\parallel 1$   |           |                                      | C                         |

| <b>OUTPUT</b>                             |                                                                 |                 |                 |           |                                      |                           |

| Linear output voltage: low                | $T_A = 25^\circ\text{C}$                                        | $V_{S-} + 0.1$  | $V_{S+} + 0.2$  |           | V                                    | A                         |

|                                           | $T_A = -40^\circ\text{C}$ to $125^\circ\text{C}$                | $V_{S-} + 0.1$  | $V_{S+} + 0.2$  |           |                                      | B                         |

| Linear output voltage: high               | $T_A = 25^\circ\text{C}$                                        | $V_{S+} - 0.25$ | $V_{S+} - 0.12$ |           | V                                    | A                         |

|                                           | $T_A = -40^\circ\text{C}$ to $125^\circ\text{C}$                | $V_{S+} - 0.25$ | $V_{S+} - 0.12$ |           |                                      | B                         |

| Output saturation voltage: high/low       |                                                                 | 120/100         |                 |           | mV                                   | C                         |

| Linear output current drive               | $T_A = 25^\circ\text{C}$                                        | $\pm 15$        | $\pm 25$        |           | $\text{mA}$                          | A                         |

|                                           | $T_A = -40^\circ\text{C}$ to $125^\circ\text{C}$                | $\pm 15$        |                 |           |                                      | B                         |

(2) Input offset voltage drift, input bias current drift, and input offset current drift are average values calculated by taking data at the end points, computing the difference, and dividing by the temperature range.

## Electrical Characteristics: $V_S = 5$ V (continued)

Test conditions at  $T_A = +25^\circ\text{C}$ ,  $V_{S+} = 5$  V,  $V_{S-} = 0$  V,  $V_{OCM} = \text{open}$ ,  $V_{OUT} = 2$  V<sub>PP</sub>,  $R_F = 2$  k $\Omega$ ,  $R_L = 2$  k $\Omega$  differential,  $G = 1$  V/V, single-ended input, differential output, and input and output referenced to mid-supply, unless otherwise noted.

| PARAMETER                                                        | TEST CONDITIONS                                                                             | MIN  | TYP              | MAX           | UNIT                      | TEST LEVEL <sup>(1)</sup> |

|------------------------------------------------------------------|---------------------------------------------------------------------------------------------|------|------------------|---------------|---------------------------|---------------------------|

| <b>POWER SUPPLY</b>                                              |                                                                                             |      |                  |               |                           |                           |

| Specified operating voltage                                      |                                                                                             | 2.5  | 5.5              | V             |                           | B                         |

| Quiescent operating current/ch                                   | $T_A = 25^\circ\text{C}$ , $\overline{PD} = V_{S+}$                                         | 250  | 350              | $\mu\text{A}$ |                           | A                         |

|                                                                  | $T_A = -40^\circ\text{C}$ to $125^\circ\text{C}$ , $\overline{PD} = V_{S+}$                 | 290  | 390              |               |                           | B                         |

| Power-supply rejection (PSRR)                                    |                                                                                             | 87   | 108              |               | dB                        | A                         |

| <b>POWER DOWN</b>                                                |                                                                                             |      |                  |               |                           |                           |

| Enable voltage threshold                                         | Specified on above 2.1 V                                                                    |      | 2.1              |               | V                         | A                         |

| Disable voltage threshold                                        | Specified off below 0.7 V                                                                   | 0.7  |                  |               | V                         | A                         |

| Disable pin bias current                                         | $\overline{PD} = V_{S-} + 0.5$ V                                                            | 50   | 500              | nA            |                           | A                         |

| Power-down quiescent current                                     | $\overline{PD} = V_{S-} + 0.5$ V                                                            | 0.5  | 2                | $\mu\text{A}$ |                           | A                         |

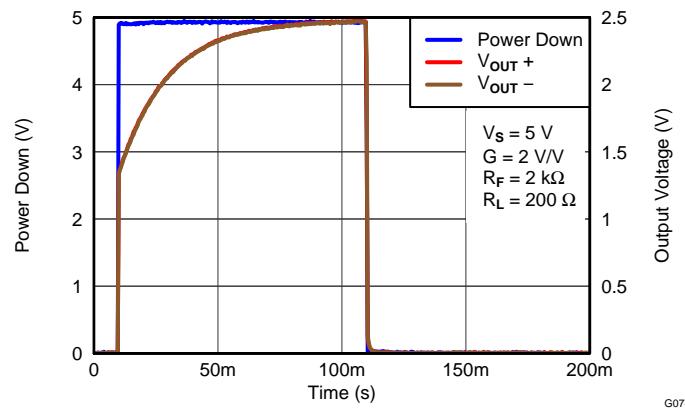

| Turn-on time delay                                               | Time from $\overline{PD}$ = high to $V_{OUT} = 90\%$ of final value, $R_L = 200$ $\Omega$   | 600  |                  | ns            |                           | C                         |

| Turn-off time delay                                              | Time from $\overline{PD}$ = low to $V_{OUT} = 10\%$ of original value, $R_L = 200$ $\Omega$ | 15   |                  | ns            |                           | C                         |

| <b>OUTPUT COMMON-MODE VOLTAGE CONTROL (<math>V_{OCM}</math>)</b> |                                                                                             |      |                  |               |                           |                           |

| Small-signal bandwidth                                           | $V_{OCM}$ input = 100 mV <sub>PP</sub>                                                      | 24   |                  |               | MHz                       | C                         |

| Slew rate                                                        | $V_{OCM}$ input = 1 V <sub>STEP</sub>                                                       | 15   |                  |               | V/ $\mu$ s                | C                         |

| Gain                                                             |                                                                                             | 0.99 | 0.996            | 1.01          | V/V                       | A                         |

| Common-mode offset voltage                                       | Offset = output common-mode voltage – $V_{OCM}$ input voltage                               |      | $\pm 1$          | $\pm 5$       | mV                        | A                         |

| $V_{OCM}$ input bias current                                     | $V_{OCM} = (V_{S+} - V_{S-})/2$                                                             |      | $\pm 20$         | $\pm 120$     | nA                        | A                         |

| $V_{OCM}$ input voltage range                                    |                                                                                             | 0.95 | 0.75 to 4.15     | 4.0           | V                         | A                         |

| $V_{OCM}$ input impedance                                        |                                                                                             | 65   | $\parallel 0.86$ |               | k $\Omega$ $\parallel$ pF | C                         |

| Default voltage offset from $(V_{S+} - V_{S-})/2$                | Offset = output common-mode voltage – $(V_{S+} - V_{S-})/2$                                 |      | $\pm 3$          | $\pm 10$      | mV                        | A                         |

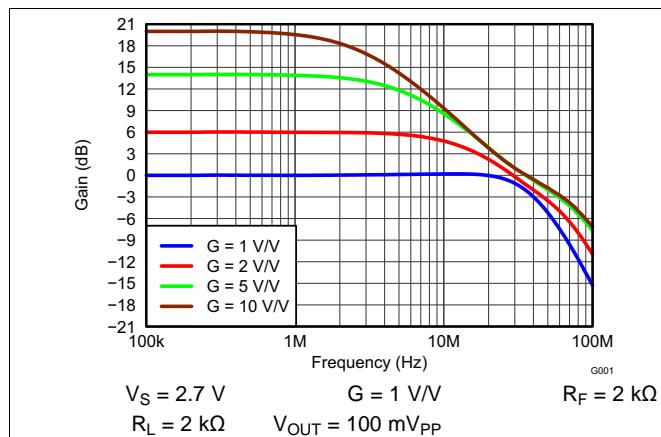

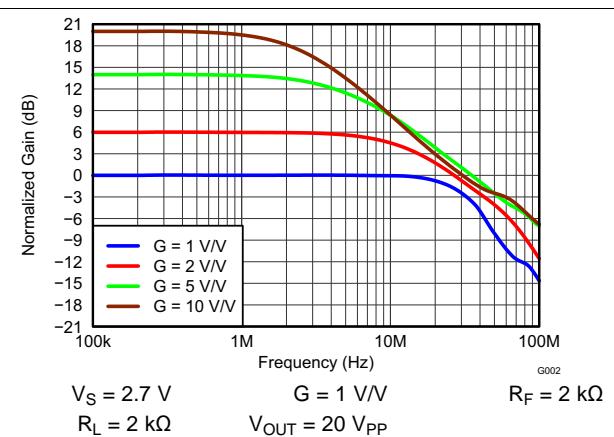

## 7.7 Typical Characteristics

**Table 3. Table of Graphs**

| DESCRIPTION                                                         | $V_S = 2.7 \text{ V}$     | $V_S = 5 \text{ V}$       |

|---------------------------------------------------------------------|---------------------------|---------------------------|

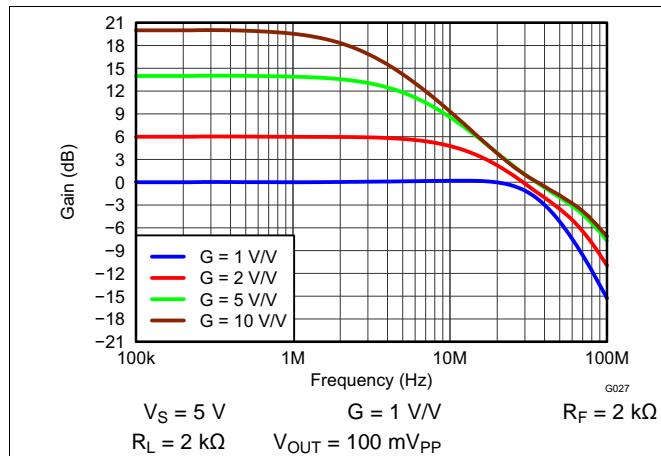

| Small-signal frequency response                                     | <a href="#">Figure 1</a>  | <a href="#">Figure 35</a> |

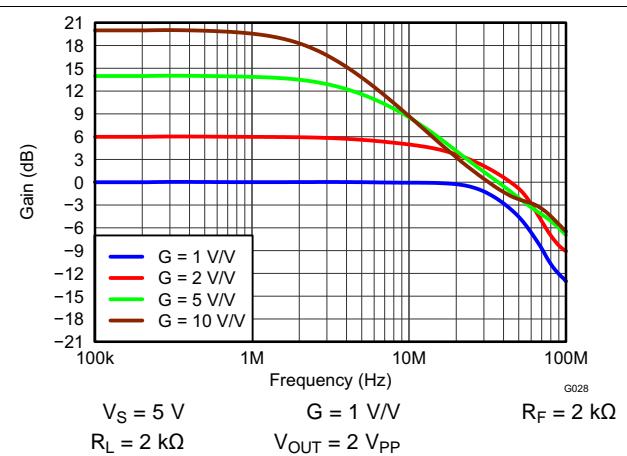

| Large-signal frequency response                                     | <a href="#">Figure 2</a>  | <a href="#">Figure 36</a> |

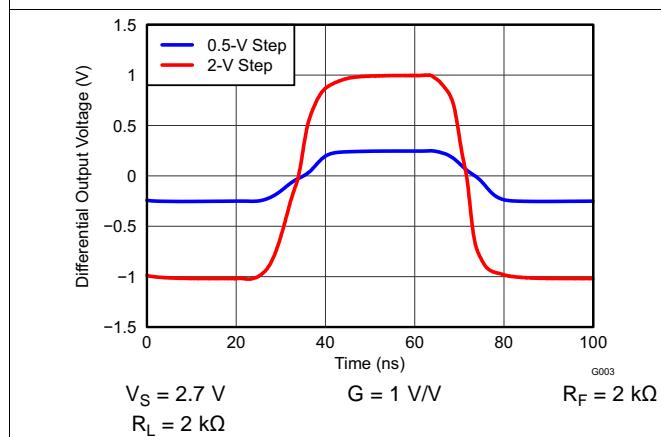

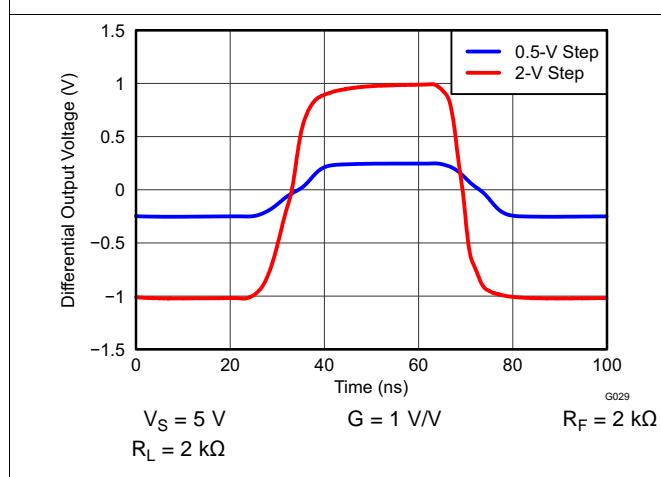

| Large- and small- signal pulse response                             | <a href="#">Figure 3</a>  | <a href="#">Figure 37</a> |

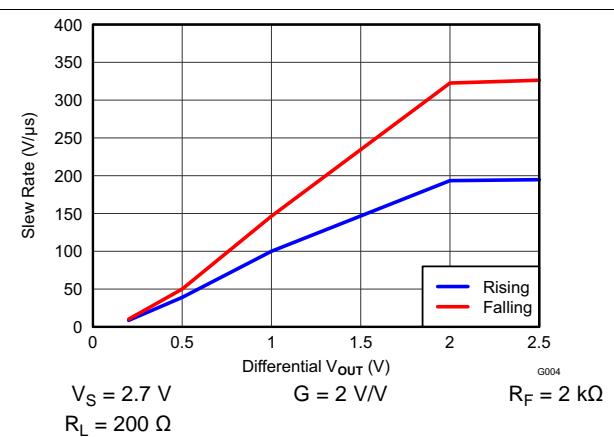

| Single-ended slew rate vs $V_{\text{OUT}}$ step                     | <a href="#">Figure 4</a>  | <a href="#">Figure 38</a> |

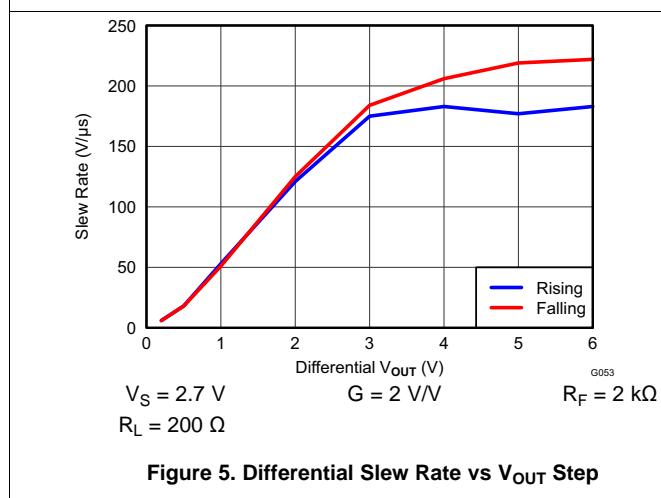

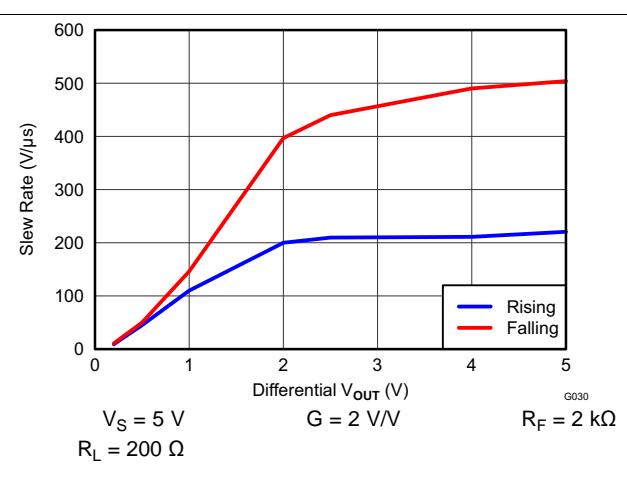

| Differential slew rate vs $V_{\text{OUT}}$ step                     | <a href="#">Figure 5</a>  | <a href="#">Figure 39</a> |

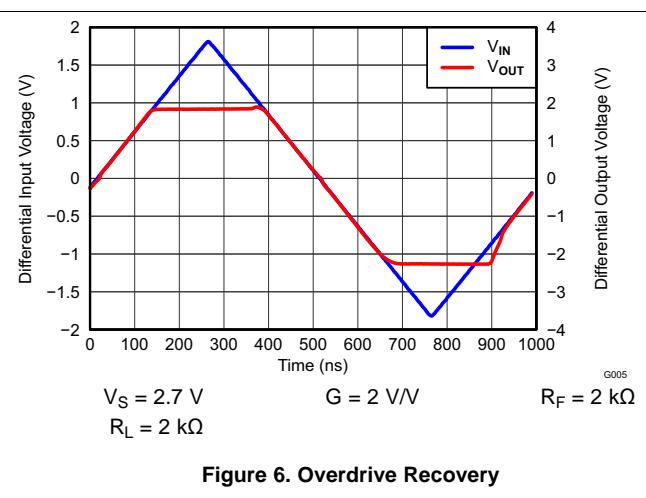

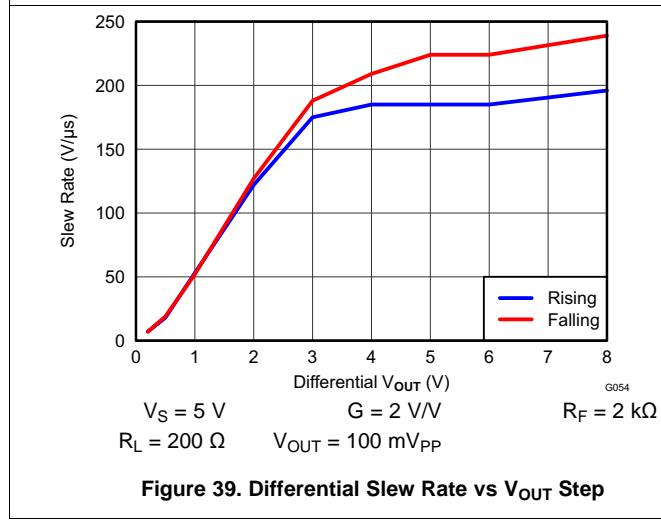

| Overdrive recovery                                                  | <a href="#">Figure 6</a>  | <a href="#">Figure 40</a> |

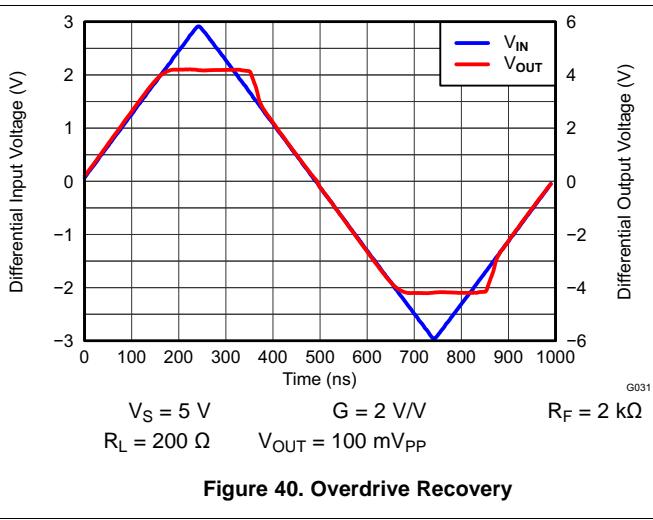

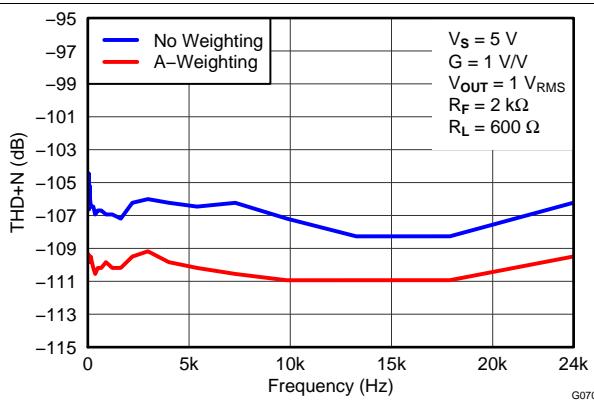

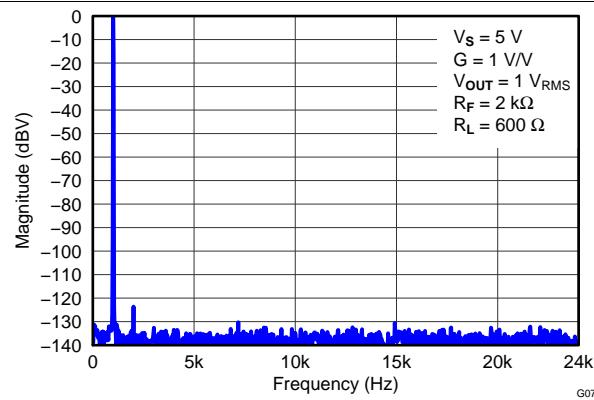

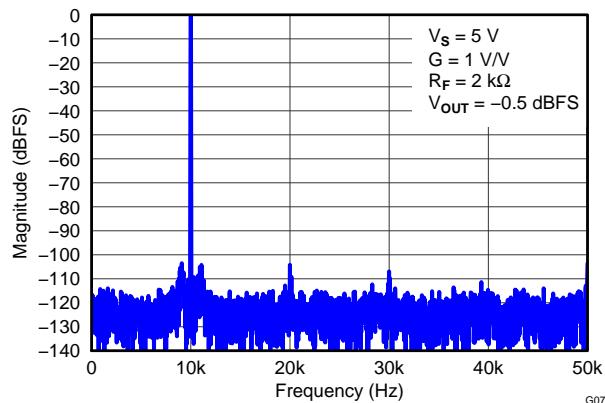

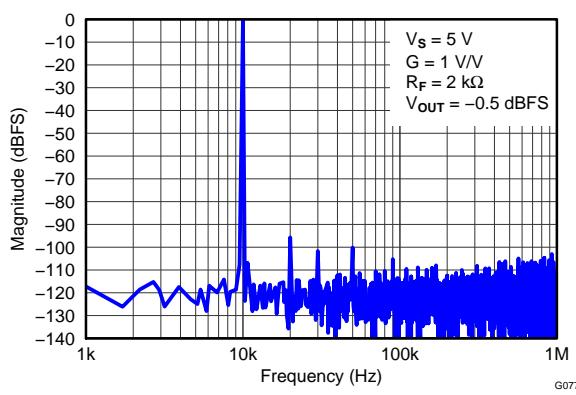

| 10-kHz FFT on audio analyzer                                        | <a href="#">Figure 7</a>  | <a href="#">Figure 41</a> |

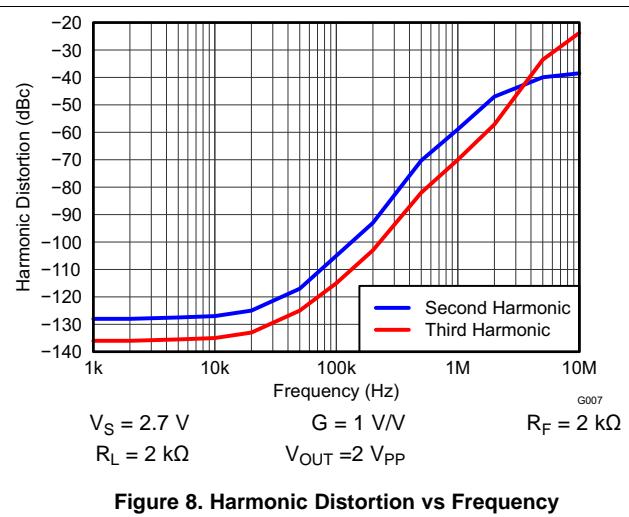

| Harmonic distortion vs Frequency                                    | <a href="#">Figure 8</a>  | <a href="#">Figure 42</a> |

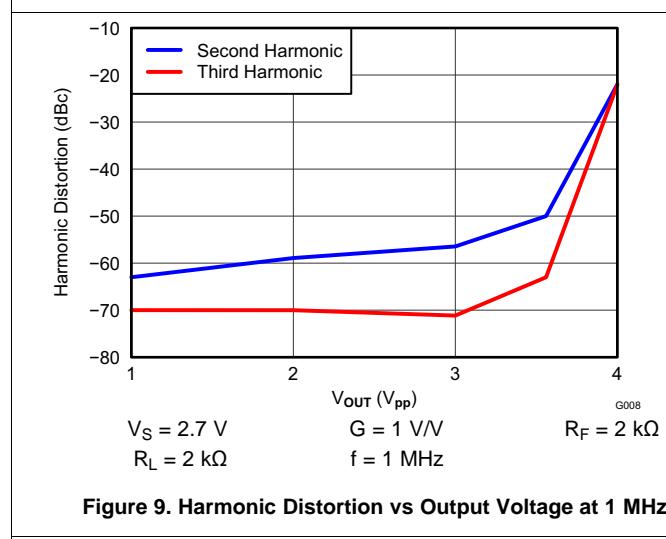

| Harmonic distortion vs Output voltage at 1 MHz                      | <a href="#">Figure 9</a>  | <a href="#">Figure 43</a> |

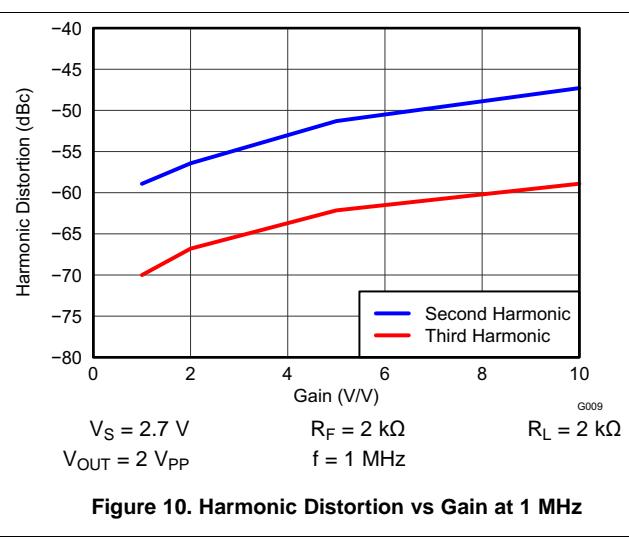

| Harmonic distortion vs Gain at 1 MHz                                | <a href="#">Figure 10</a> | <a href="#">Figure 44</a> |

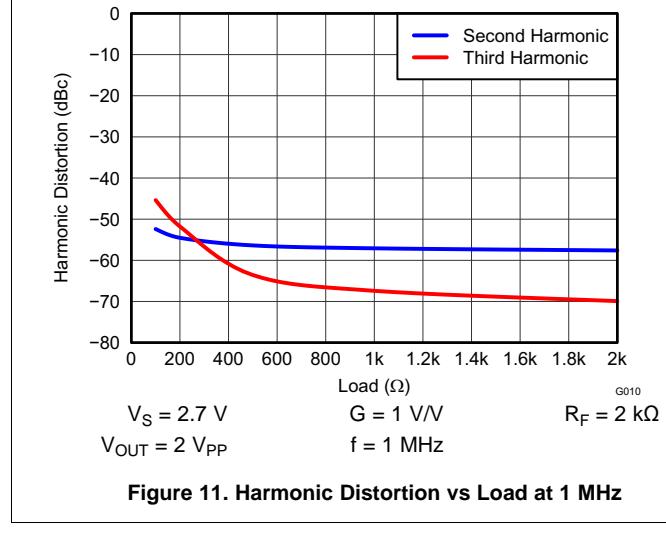

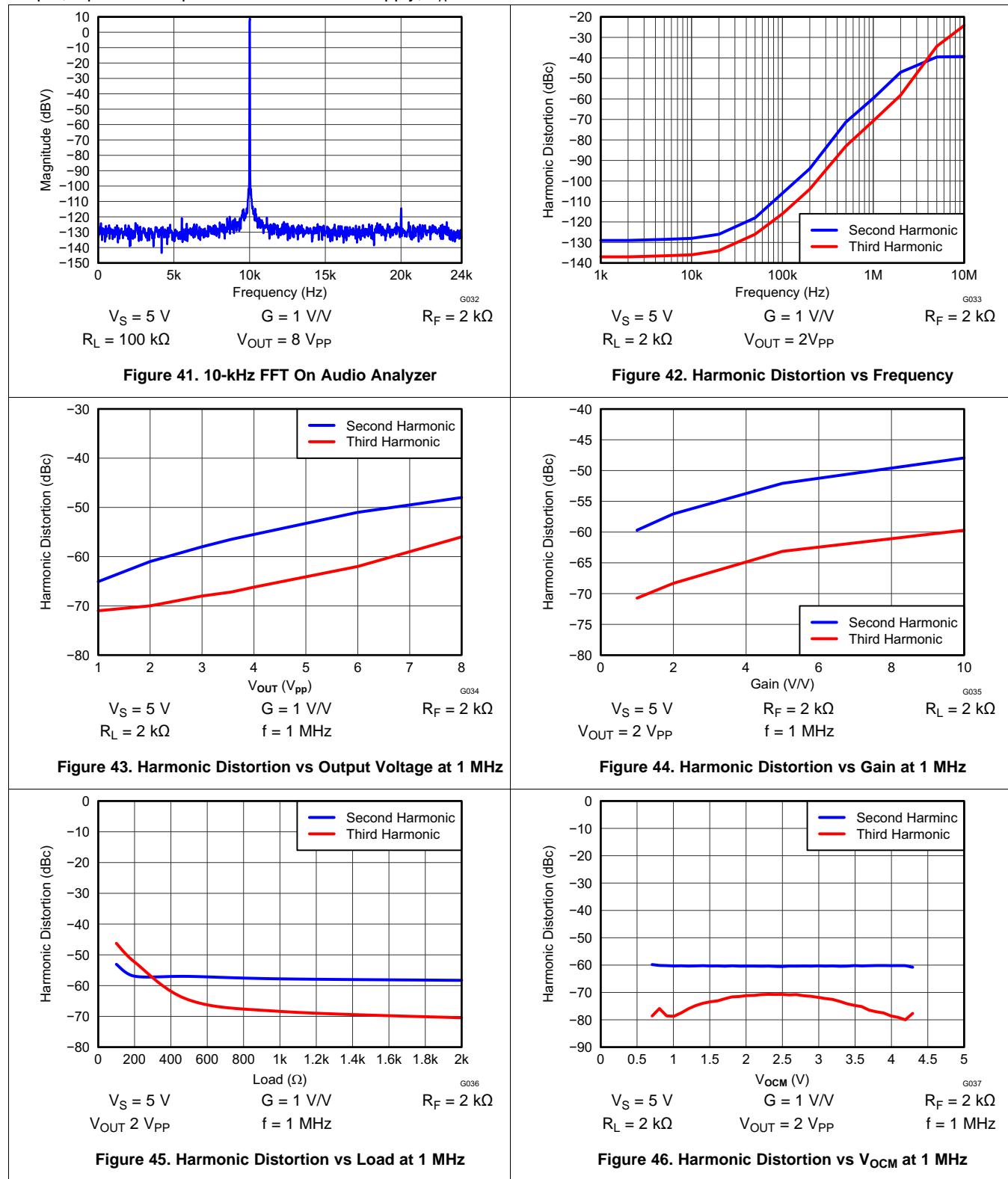

| Harmonic distortion vs Load at 1 MHz                                | <a href="#">Figure 11</a> | <a href="#">Figure 45</a> |

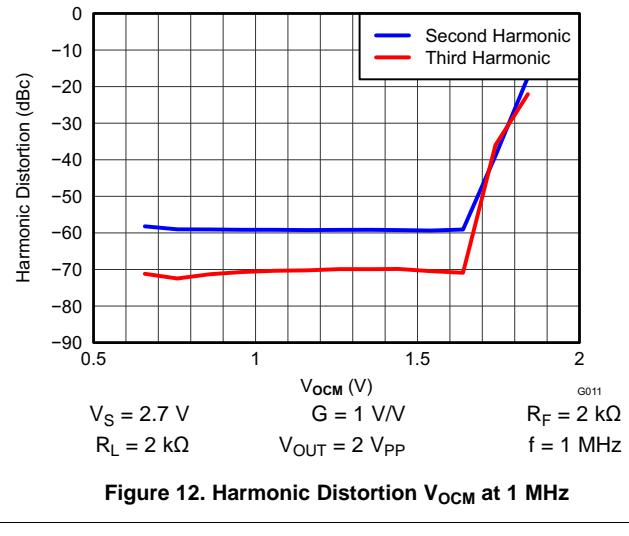

| Harmonic distortion vs $V_{\text{OCM}}$ at 1 MHz                    | <a href="#">Figure 12</a> | <a href="#">Figure 46</a> |

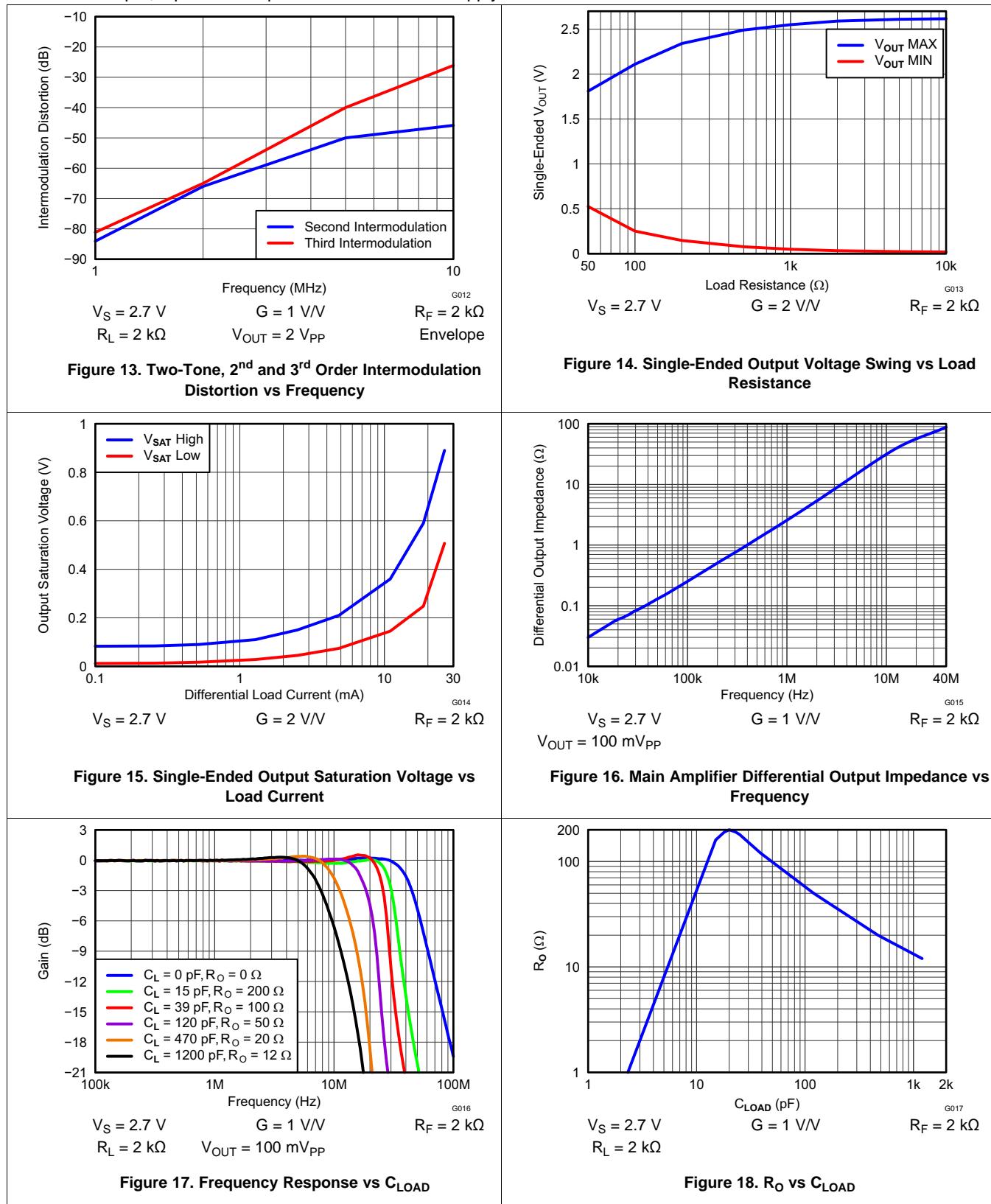

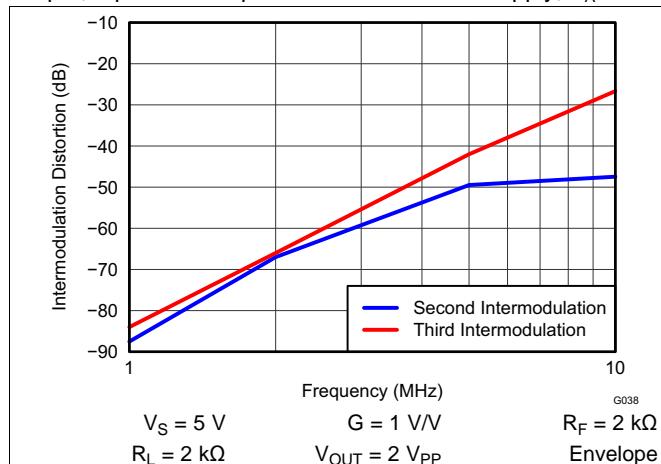

| Two-tone, 2nd and 3rd order intermodulation distortion vs Frequency | <a href="#">Figure 13</a> | <a href="#">Figure 47</a> |

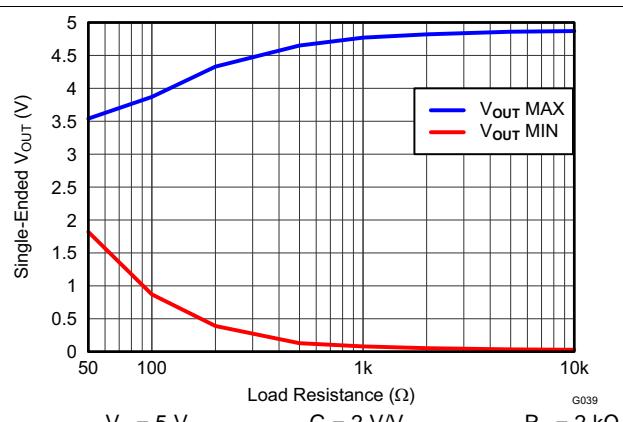

| Single-ended output voltage swing vs Load resistance                | <a href="#">Figure 14</a> | <a href="#">Figure 48</a> |

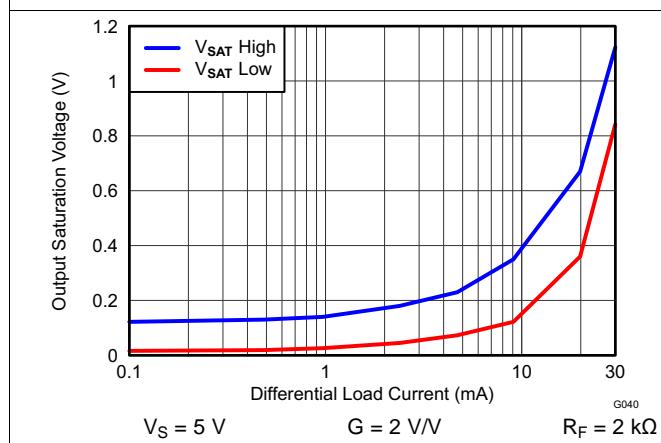

| Single-ended output saturation voltage vs Load current              | <a href="#">Figure 15</a> | <a href="#">Figure 49</a> |

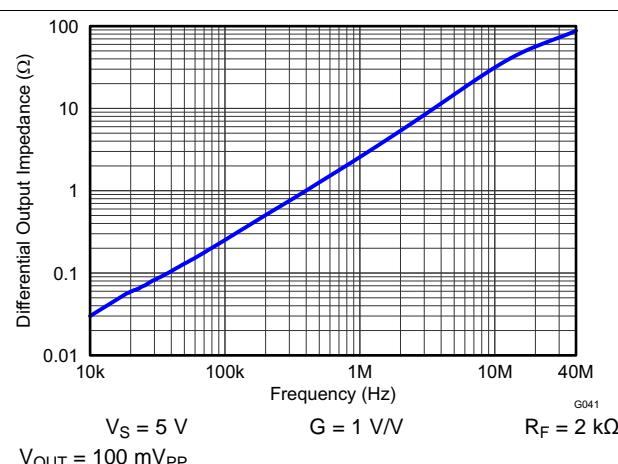

| Main amplifier differential output impedance vs Frequency           | <a href="#">Figure 16</a> | <a href="#">Figure 50</a> |

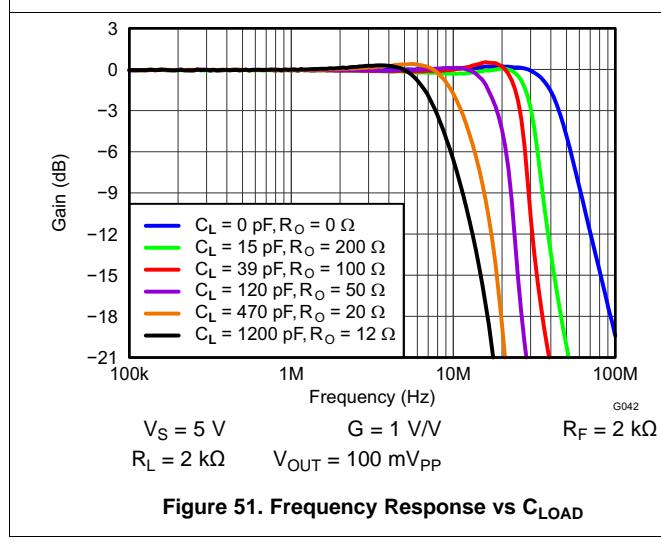

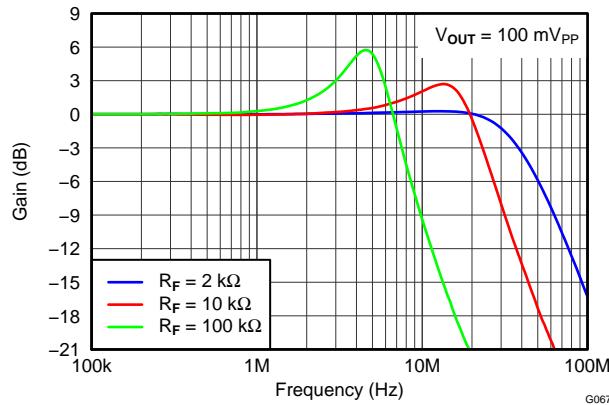

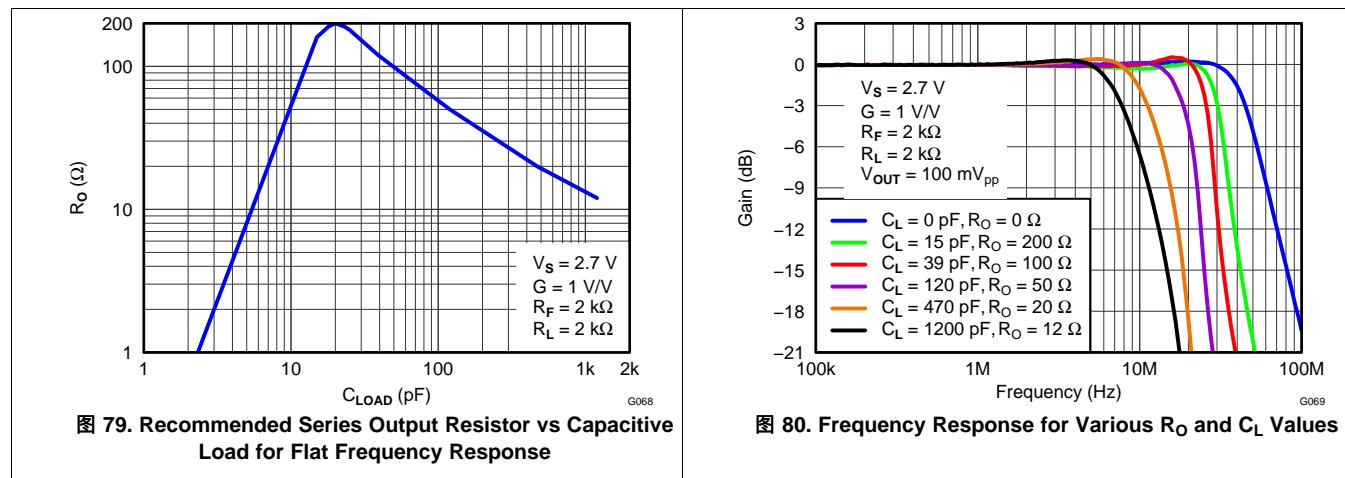

| Frequency response vs $C_{\text{LOAD}}$                             | <a href="#">Figure 17</a> | <a href="#">Figure 51</a> |

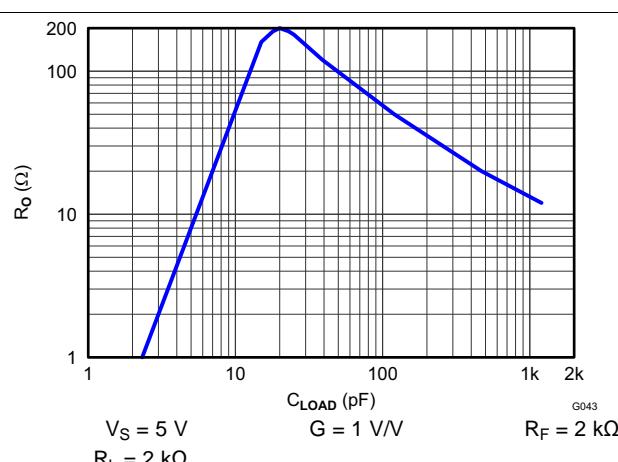

| $R_O$ vs $C_{\text{LOAD}}$                                          | <a href="#">Figure 18</a> | <a href="#">Figure 52</a> |

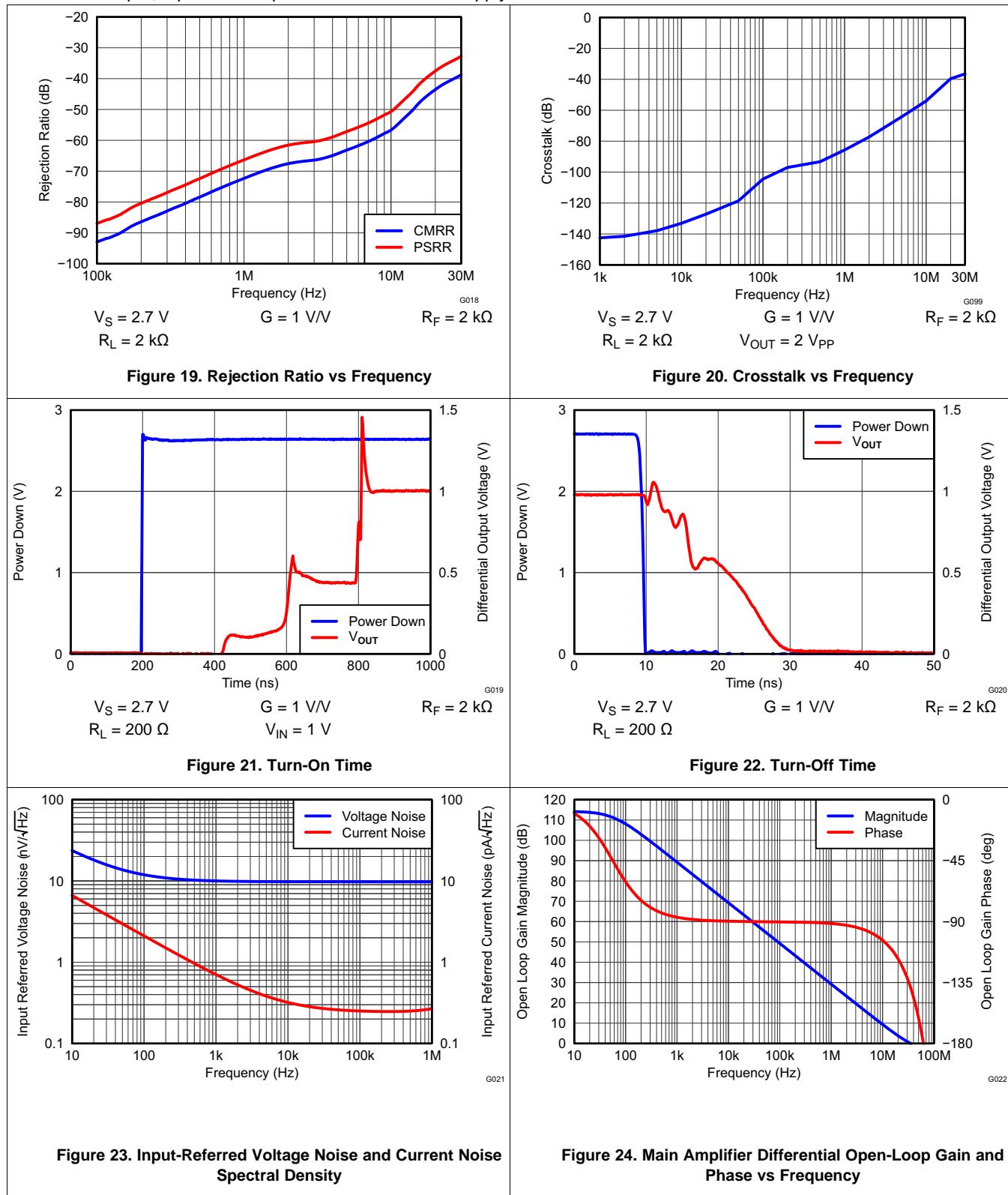

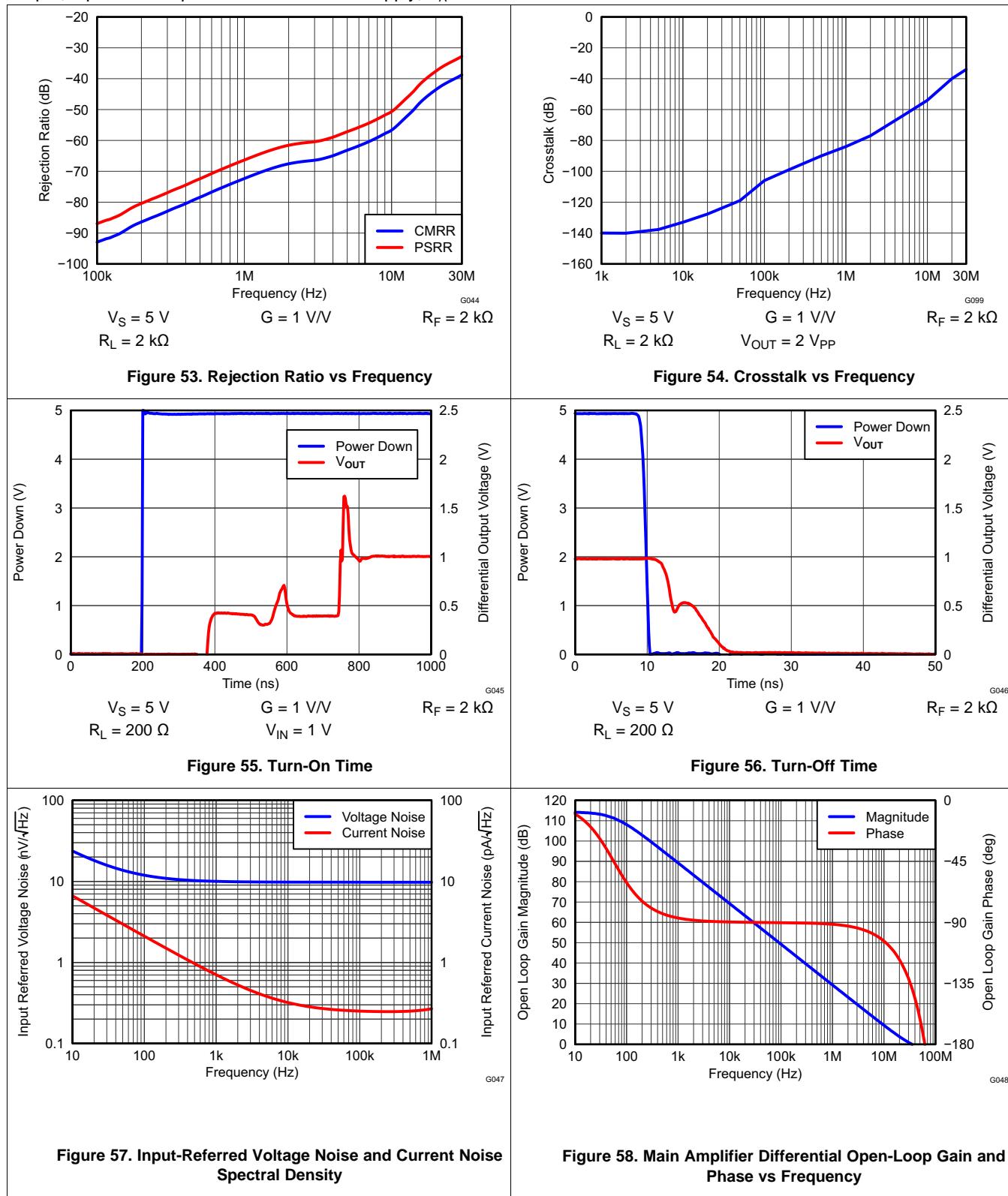

| Rejection ratio vs Frequency                                        | <a href="#">Figure 19</a> | <a href="#">Figure 53</a> |

| Crosstalk vs Frequency                                              | <a href="#">Figure 20</a> | <a href="#">Figure 54</a> |

| Turn-on time                                                        | <a href="#">Figure 21</a> | <a href="#">Figure 55</a> |

| Turn-off time                                                       | <a href="#">Figure 22</a> | <a href="#">Figure 56</a> |

| Input-referred voltage noise and current noise spectral density     | <a href="#">Figure 23</a> | <a href="#">Figure 57</a> |

| Main amplifier differential open-loop gain and phase vs Frequency   | <a href="#">Figure 24</a> | <a href="#">Figure 58</a> |

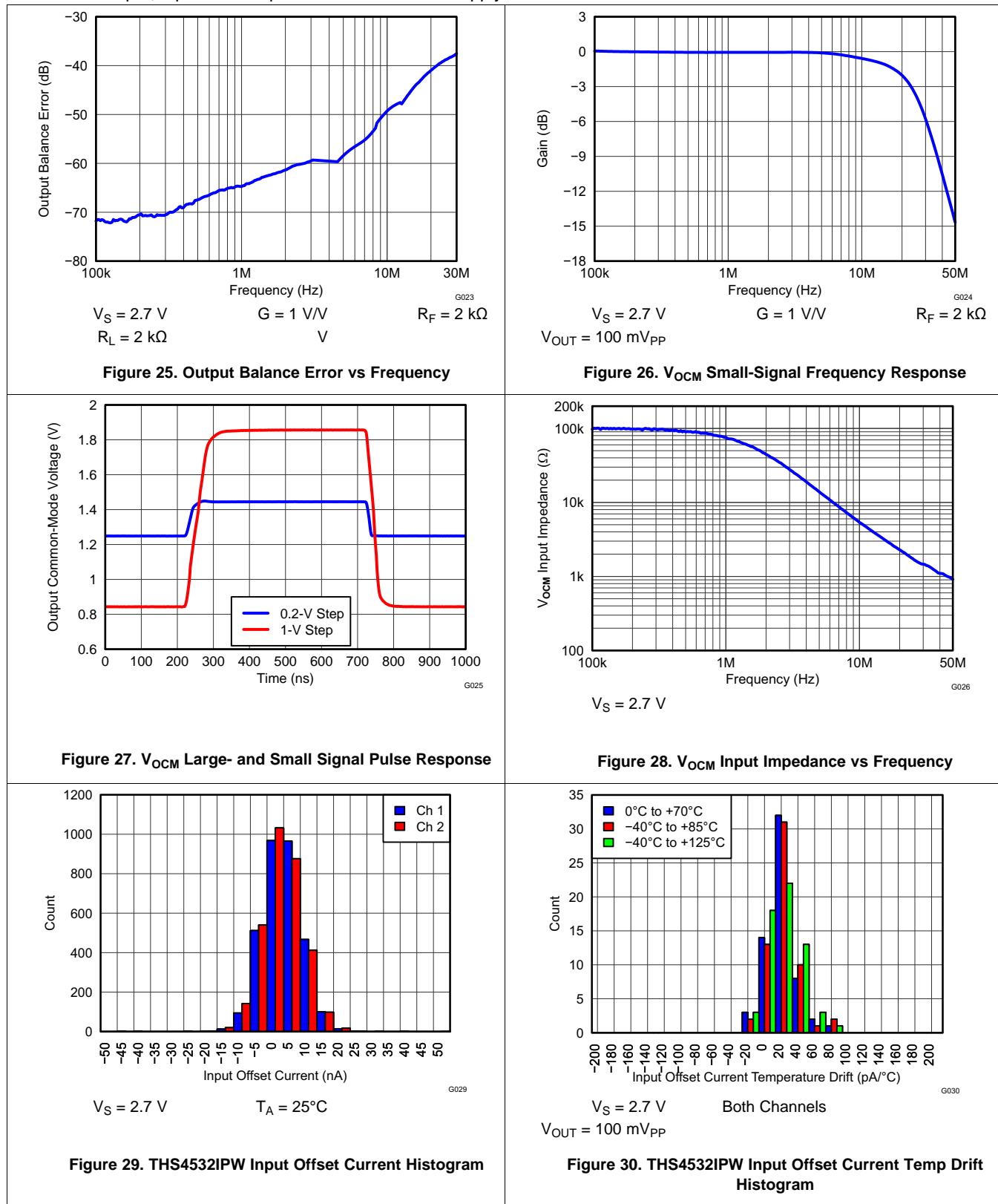

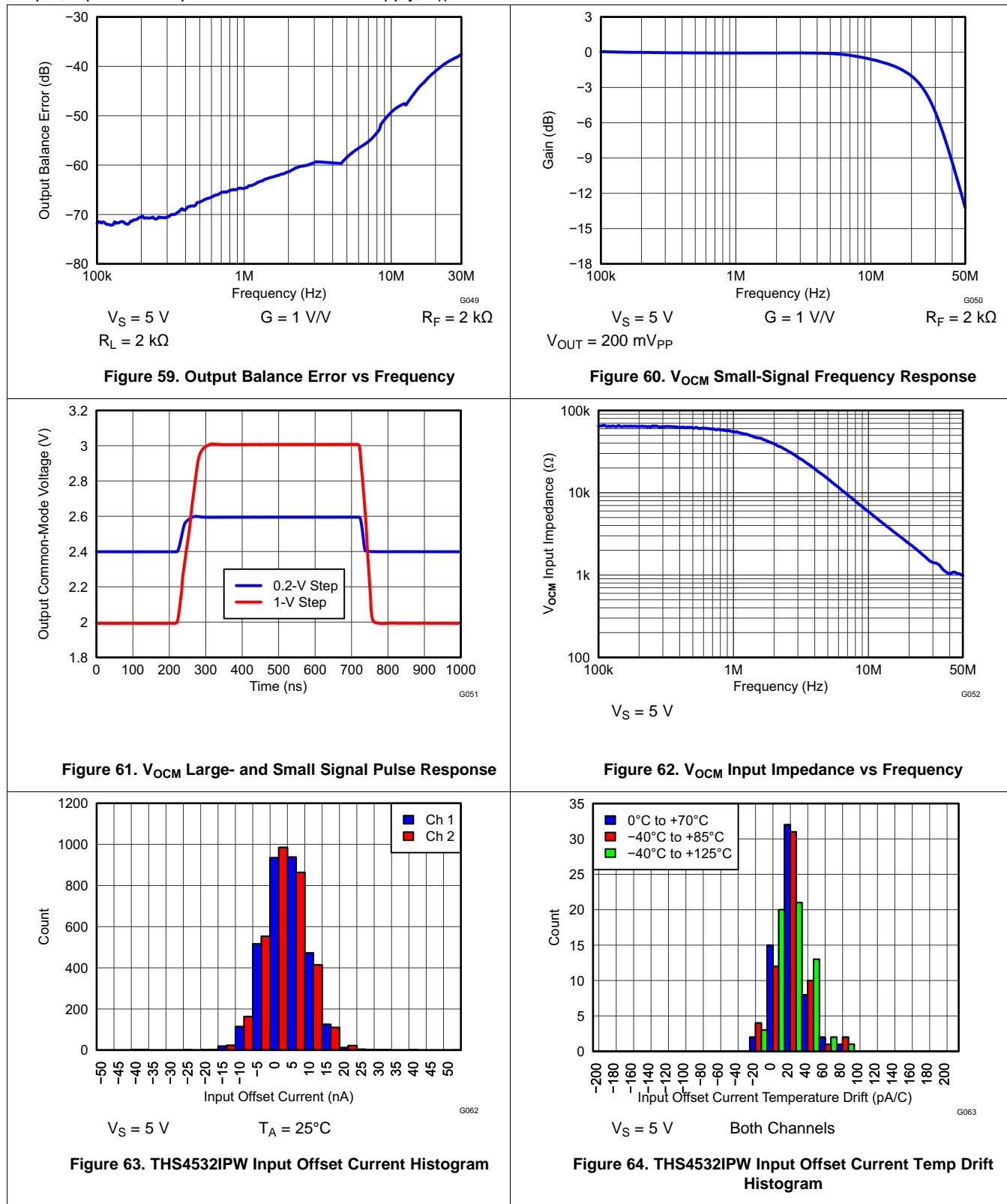

| Output balance error vs Frequency                                   | <a href="#">Figure 25</a> | <a href="#">Figure 59</a> |

| $V_{\text{OCM}}$ small signal frequency response                    | <a href="#">Figure 26</a> | <a href="#">Figure 60</a> |

| $V_{\text{OCM}}$ large and small signal pulse response              | <a href="#">Figure 27</a> | <a href="#">Figure 61</a> |

| $V_{\text{OCM}}$ input impedance vs frequency                       | <a href="#">Figure 28</a> | <a href="#">Figure 62</a> |

| Count vs input offset current                                       | <a href="#">Figure 29</a> | <a href="#">Figure 63</a> |

| Count vs input offset current temperature drift                     | <a href="#">Figure 30</a> | <a href="#">Figure 64</a> |

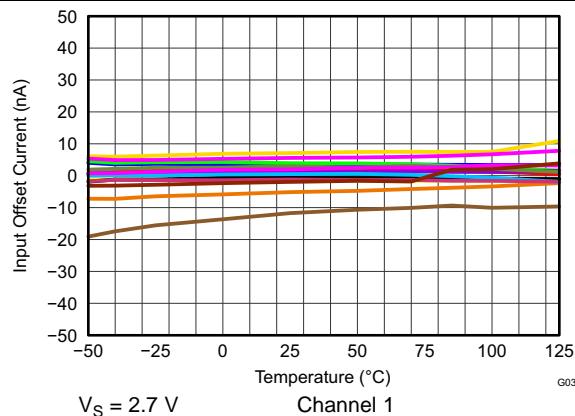

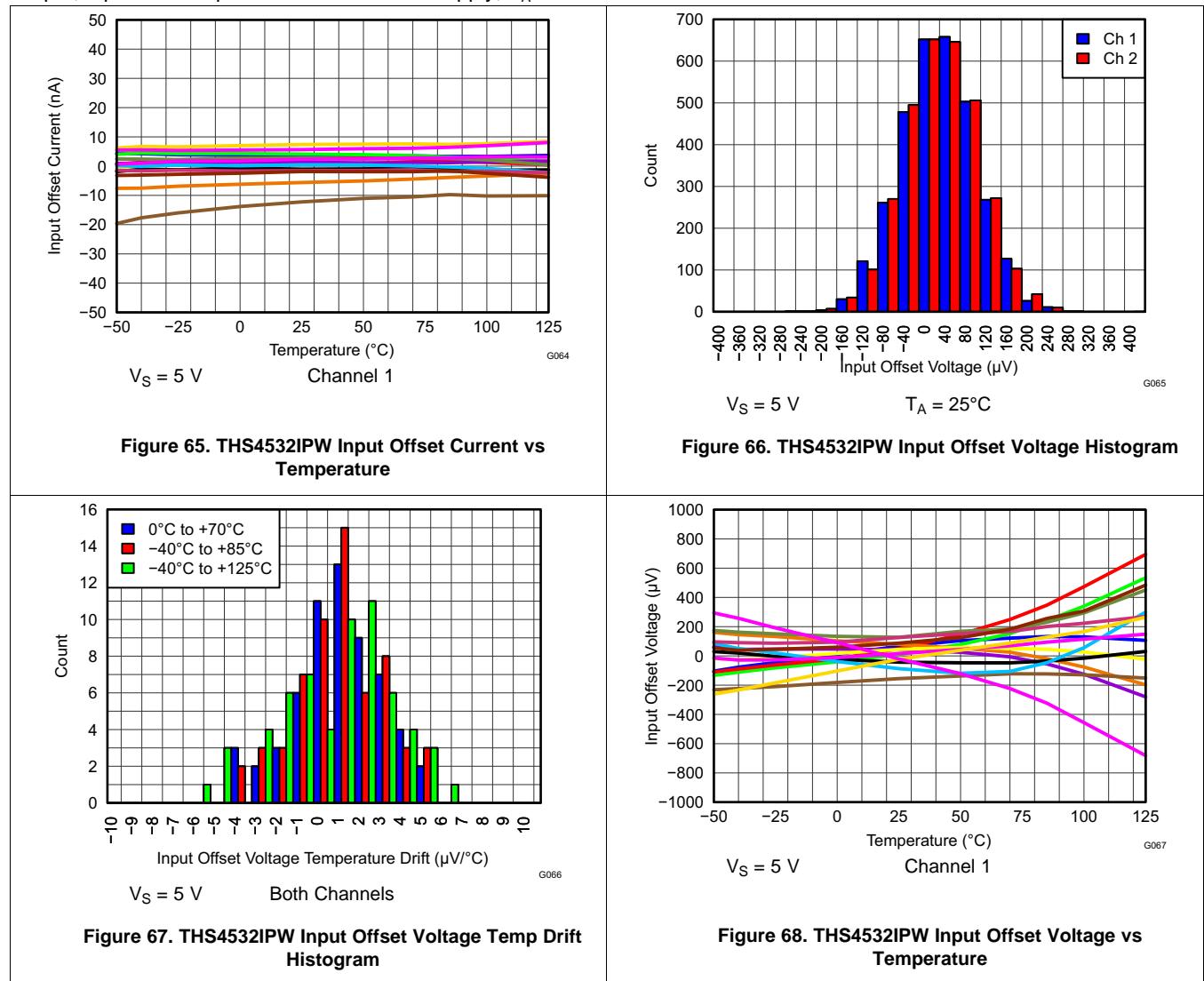

| Input offset current vs temperature                                 | <a href="#">Figure 31</a> | <a href="#">Figure 65</a> |

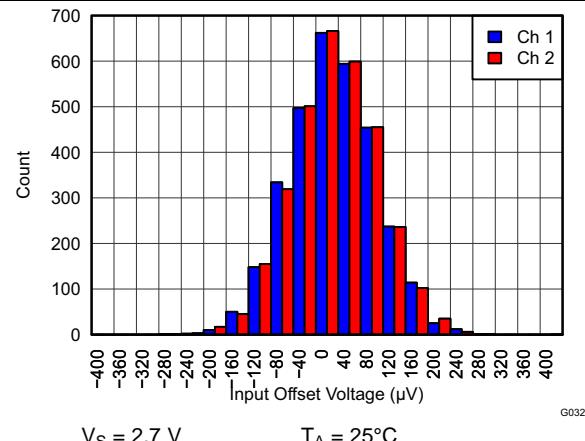

| Count vs input offset voltage                                       | <a href="#">Figure 32</a> | <a href="#">Figure 66</a> |

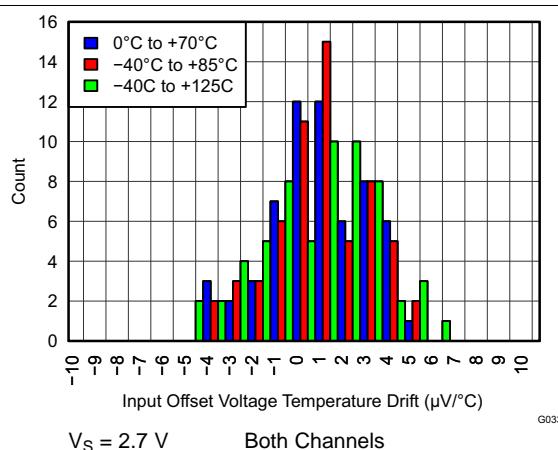

| Count vs input offset voltage temperature drift                     | <a href="#">Figure 33</a> | <a href="#">Figure 67</a> |

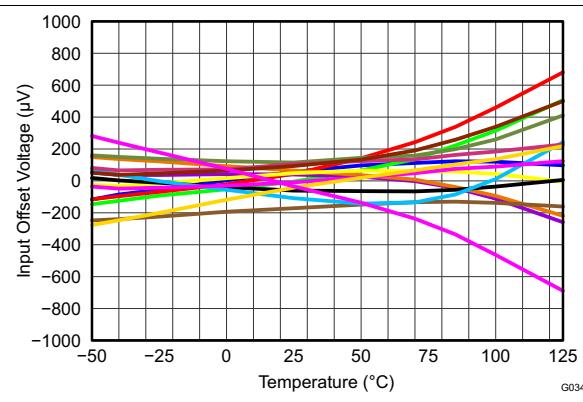

| Input offset voltage vs temperature                                 | <a href="#">Figure 34</a> | <a href="#">Figure 68</a> |

### 7.7.1 Typical Characteristics: $V_S = 2.7$ V

$V_{S+} = 2.7$  V,  $V_{S-} = 0$  V, CM = open,  $V_{OUT} = 2$  Vpp,  $R_F = 2$  k $\Omega$ ,  $R_L = 2$  k $\Omega$  Differential,  $G = 1$  V/V, Single-Ended Input, Differential Output, Input and Output Referenced to mid-supply unless otherwise noted.

Figure 1. Small-Signal Frequency Response

Figure 2. Large-Signal Frequency Response

Figure 3. Large- and Small-Signal Pulse Response

Figure 4. Single-Ended Slew Rate vs  $V_{OUT}$  Step

Figure 5. Differential Slew Rate vs  $V_{OUT}$  Step

Figure 6. Overdrive Recovery

## Typical Characteristics: $V_S = 2.7$ V (continued)

$V_{S+} = 2.7$  V,  $V_{S-} = 0$  V, CM = open,  $V_{OUT} = 2$  Vpp,  $R_F = 2$  k $\Omega$ ,  $R_L = 2$  k $\Omega$  Differential,  $G = 1$  V/V, Single-Ended Input, Differential Output, Input and Output Referenced to mid-supply unless otherwise noted.

## Typical Characteristics: $V_S = 2.7$ V (continued)

$V_{S+} = 2.7$  V,  $V_{S-} = 0$  V, CM = open,  $V_{OUT} = 2$  Vpp,  $R_F = 2$  k $\Omega$ ,  $R_L = 2$  k $\Omega$  Differential,  $G = 1$  V/V, Single-Ended Input, Differential Output, Input and Output Referenced to mid-supply unless otherwise noted.

## Typical Characteristics: $V_S = 2.7$ V (continued)

$V_{S+} = 2.7$  V,  $V_{S-} = 0$  V, CM = open,  $V_{OUT} = 2$  Vpp,  $R_F = 2$  k $\Omega$ ,  $R_L = 2$  k $\Omega$  Differential,  $G = 1$  V/V, Single-Ended Input, Differential Output, Input and Output Referenced to mid-supply unless otherwise noted.

## Typical Characteristics: $V_S = 2.7$ V (continued)

$V_{S+} = 2.7$  V,  $V_{S-} = 0$  V, CM = open,  $V_{OUT} = 2$  Vpp,  $R_F = 2$  k $\Omega$ ,  $R_L = 2$  k $\Omega$  Differential,  $G = 1$  V/V, Single-Ended Input, Differential Output, Input and Output Referenced to mid-supply unless otherwise noted.

## Typical Characteristics: $V_S = 2.7$ V (continued)

$V_{S+} = 2.7$  V,  $V_{S-} = 0$  V, CM = open,  $V_{OUT} = 2$  Vpp,  $R_F = 2$  k $\Omega$ ,  $R_L = 2$  k $\Omega$  Differential,  $G = 1$  V/V, Single-Ended Input, Differential Output, Input and Output Referenced to mid-supply unless otherwise noted.

Figure 31. THS4532IPW Input Offset Current vs Temperature

Figure 32. THS4532IPW Input Offset Voltage Histogram

Figure 33. THS4532IPW Input Offset Voltage Temp Drift Histogram

Figure 34. THS4532IPW Input Offset Voltage vs Temperature

### 7.7.2 Typical Characteristics: $V_S = 5$ V

$V_{S+} = 5$  V,  $V_{S-} = 0$  V,  $V_{OCM} = \text{open}$ ,  $V_{OUT} = 2$  Vpp,  $R_F = 2$  k $\Omega$ ,  $R_L = 2$  k $\Omega$  Differential,  $G = 1$  V/V, Single-Ended Input, Differential Output, Input and Output Referenced to mid-supply,  $T_A = 25^\circ\text{C}$  unless otherwise noted.

Figure 35. Small-Signal Frequency Response

Figure 36. Large-Signal Frequency Response

Figure 37. Large- and Small-Signal Pulse Response

Figure 38. Single-Ended Slew Rate vs  $V_{OUT}$  Step

Figure 39. Differential Slew Rate vs  $V_{OUT}$  Step

Figure 40. Overdrive Recovery

## Typical Characteristics: $V_S = 5$ V (continued)

$V_{S+} = 5$  V,  $V_{S-} = 0$  V,  $V_{OCM} = \text{open}$ ,  $V_{OUT} = 2$  V<sub>pp</sub>,  $R_F = 2$  k $\Omega$ ,  $R_L = 2$  k $\Omega$  Differential,  $G = 1$  V/V, Single-Ended Input, Differential Output, Input and Output Referenced to mid-supply,  $T_A = 25^\circ\text{C}$  unless otherwise noted.

## Typical Characteristics: $V_S = 5$ V (continued)

$V_{S+} = 5$  V,  $V_{S-} = 0$  V,  $V_{OCM} = \text{open}$ ,  $V_{OUT} = 2$  Vpp,  $R_F = 2$  k $\Omega$ ,  $R_L = 2$  k $\Omega$  Differential,  $G = 1$  V/V, Single-Ended Input, Differential Output, Input and Output Referenced to mid-supply,  $T_A = 25^\circ\text{C}$  unless otherwise noted.

Figure 47. Two-Tone, 2<sup>nd</sup> and 3<sup>rd</sup> Order Intermodulation Distortion vs Frequency

Figure 48. Single-Ended Output Voltage Swing vs Load Resistance

Figure 49. Single-Ended Output Saturation Voltage vs Load Current

Figure 50. Main Amplifier Differential Output Impedance vs Frequency

Figure 51. Frequency Response vs  $C_{LOAD}$

Figure 52.  $R_O$  vs  $C_{LOAD}$

**Typical Characteristics:  $V_S = 5$  V (continued)**

$V_{S+} = 5$  V,  $V_{S-} = 0$  V,  $V_{OCM} = \text{open}$ ,  $V_{OUT} = 2$  Vpp,  $R_F = 2$  k $\Omega$ ,  $R_L = 2$  k $\Omega$  Differential,  $G = 1$  V/V, Single-Ended Input, Differential Output, Input and Output Referenced to mid-supply,  $T_A = 25^\circ\text{C}$  unless otherwise noted.

## Typical Characteristics: $V_S = 5$ V (continued)

$V_{S+} = 5$  V,  $V_{S-} = 0$  V,  $V_{OCM} = \text{open}$ ,  $V_{OUT} = 2$  Vpp,  $R_F = 2$  k $\Omega$ ,  $R_L = 2$  k $\Omega$  Differential,  $G = 1$  V/V, Single-Ended Input, Differential Output, Input and Output Referenced to mid-supply,  $T_A = 25^\circ\text{C}$  unless otherwise noted.

## Typical Characteristics: $V_S = 5$ V (continued)

$V_{S+} = 5$  V,  $V_{S-} = 0$  V,  $V_{OCM} = \text{open}$ ,  $V_{OUT} = 2$  Vpp,  $R_F = 2$  k $\Omega$ ,  $R_L = 2$  k $\Omega$  Differential,  $G = 1$  V/V, Single-Ended Input, Differential Output, Input and Output Referenced to mid-supply,  $T_A = 25^\circ\text{C}$  unless otherwise noted.

## 8 Detailed Description

## 8.1 Overview

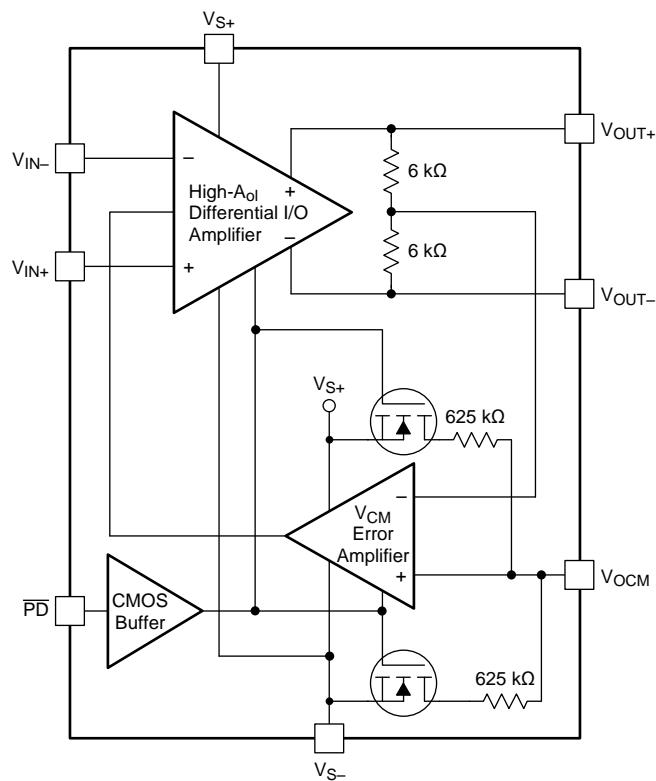

As shown in the [Functional Block Diagram](#), the THS4532 device is comprised of three functional blocks: a fully-differential amplifier with high open-loop gain of 114 dB, a servo amplifier to set the common-mode voltage of the output equal to the  $V_{OCM}$  input, and a power-down circuit to greatly reduce the power consumption when the device is idle.

The common-mode voltage servo has impressive performance specifications of  $\pm 1\%$  maximum gain error,  $\pm 5\text{-mV}$  maximum voltage offset, and 24-MHz bandwidth.

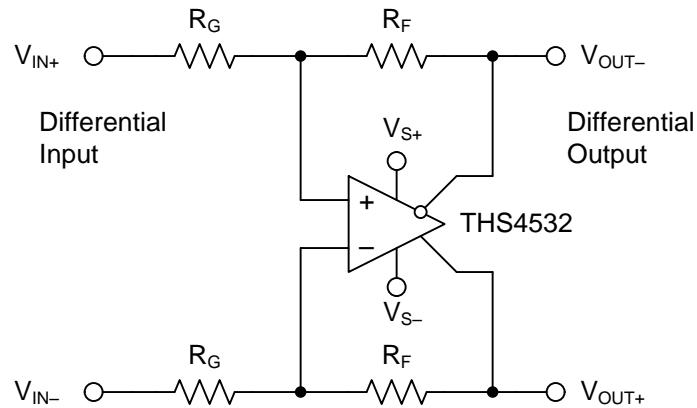

## 8.2 Functional Block Diagram

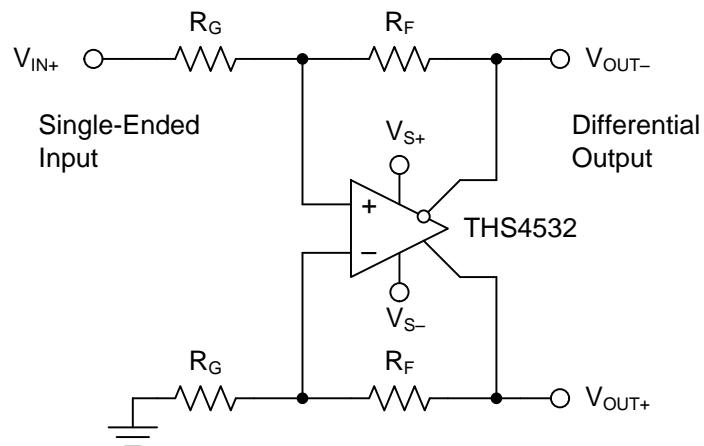

### 8.3 Feature Description

### 8.3.1 Input Common-Mode Voltage Range

The input common-mode voltage of a fully-differential amplifier is the voltage at the positive and negative (+ and -) input pins of the amplifier.

Do not violate the input common-mode voltage range ( $V_{ICR}$ ) of the amplifier. Assuming the amplifier is in linear operation, the voltage across the input pins is only a few millivolts at most. Therefore, finding the voltage at one input pin determines the input common-mode voltage of the amplifier.

Use 公式 1 to calculate the voltage with the negative input as a summing node.

$$\left( V_{OUT+} \times \frac{R_G}{R_G + R_F} \right) + \left( V_{IN-} \times \frac{R_F}{R_G + R_F} \right) \quad (1)$$

To determine the  $V_{ICR}$  of the amplifier, the voltage at the negative input is evaluated at the extremes of  $V_{OUT+}$ .

As the gain of the amplifier increases, the input common-mode voltage becomes closer and closer to the input common-mode voltage of the source.

## Feature Description (接下页)

### 8.3.1.1 Setting the Output Common-Mode Voltage

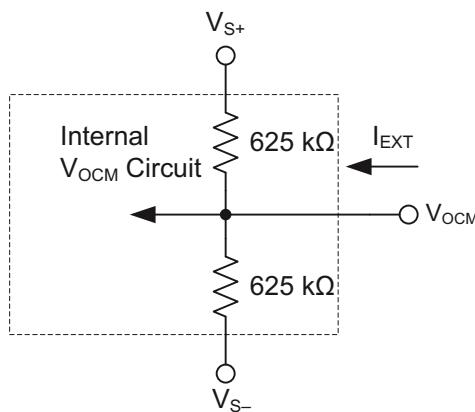

The output common-mode voltage is set by the voltage at the  $V_{OCM}$  pin and the internal circuit works to maintain the output common-mode voltage as close as possible to this voltage. If left unconnected, the output common-mode is set to mid-supply by internal circuitry, which may be over-driven from an external source. [图 69](#) is representative of the  $V_{OCM}$  input. The internal  $V_{OCM}$  circuit has about 24-MHz of –3-dB bandwidth, which is required for best performance, but it is intended to be a DC bias input pin. Bypass capacitors are recommended on this pin to reduce noise. Use [公式 2](#) to calculate the external current required to overdrive the internal resistor divider.

$$I_{EXT} = \frac{2V_{OCM} - (V_{S+} + V_{S-})}{625 \text{ k}\Omega}$$

where

- $V_{OCM}$  is the voltage applied to the  $V_{OCM}$  pin. [\(2\)](#)

图 69. Simplified  $V_{OCM}$  Input Circuit

## Feature Description (接下页)

### 8.3.2 Power Down

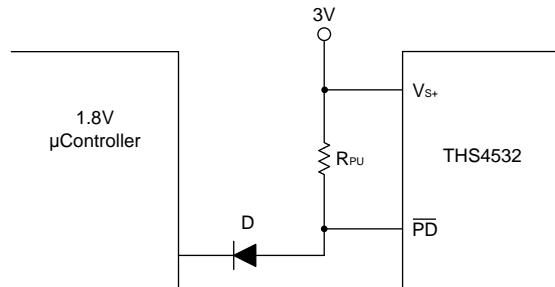

The power down pin is internally connected to a CMOS stage which must be driven to a minimum of 2.1 V to ensure proper high logic.

图 70. Simplified Power-Down Internal Circuit

If 1.8-V logic is used to drive the pin, a shoot through current of up to 100  $\mu$ A may develop in the digital logic causing the overall quiescent current to exceed the 2  $\mu$ A of maximum disabled quiescent current specified in the [Electrical Characteristics:  \$V\_S = 2.7\$  V](#).

To properly interface to 1.8-V logic with minimal increase in additional current draw, a logic-level translator like the SN74AVC1T45 device can be used.

Alternatively, the same function can be achieved using a diode and pullup resistor as shown in [图 71](#).

图 71. THS4532 Power Down Interface to 1.8-V Logic Microcontroller

The voltage at the power down pin will be a function of the supply voltage, input logic level, and diode drop. As long as the diode is forward biased, the power down voltage is calculated using [公式 3](#).

$$V_{PD} = V_L + V_f$$

where

- $V_L$  is the logic level voltage.

- $V_f$  is the forward voltage drop across the diode. (3)

This means for 1.8-V logic, the forward voltage of the diode should be greater than 0.3 V but less than 0.7 V to keep the power down logic level above 2.1 V and less than 0.7 V respectively.

For example, if 1N914 is selected as the diode with a forward voltage of approximately 0.4 V, the translated logic voltages will be 0.4 V for disabled operation and 2.2 V for enabled operation.

## Feature Description (接下页)

Use [公式 4](#) to calculate the additional current draw.

$$i_{PD} = \frac{V_{CC} - (V_L + V_f)}{R_{PU}} \quad (4)$$

[公式 2](#) shows that larger values of RPU result in a smaller additional current. A reasonable value of RPU is 500 kΩ where an additional current draw of 5.2 μA is expected while the device is in operation and 1.6 μA when disabled.

## 8.4 Device Functional Modes

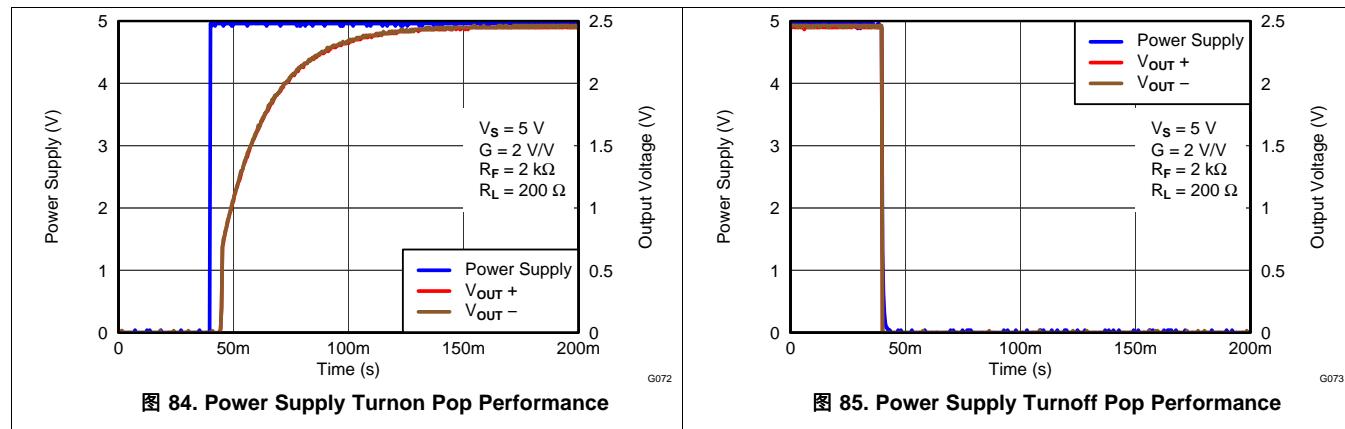

The THS4532 has two functional modes: full-power mode and power-down mode. The power-down mode reduces the quiescent current of the device to 500 nA from a typical value of 290 μA with a 5-V supply.

With a turnon time of only 600 ns and a turnoff time of 15 ns, the power-down mode can be used to greatly reduce the average power consumption of the device without sacrificing system performance.

## 9 Application and Implementation

### 注

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

### 9.1 Application Information

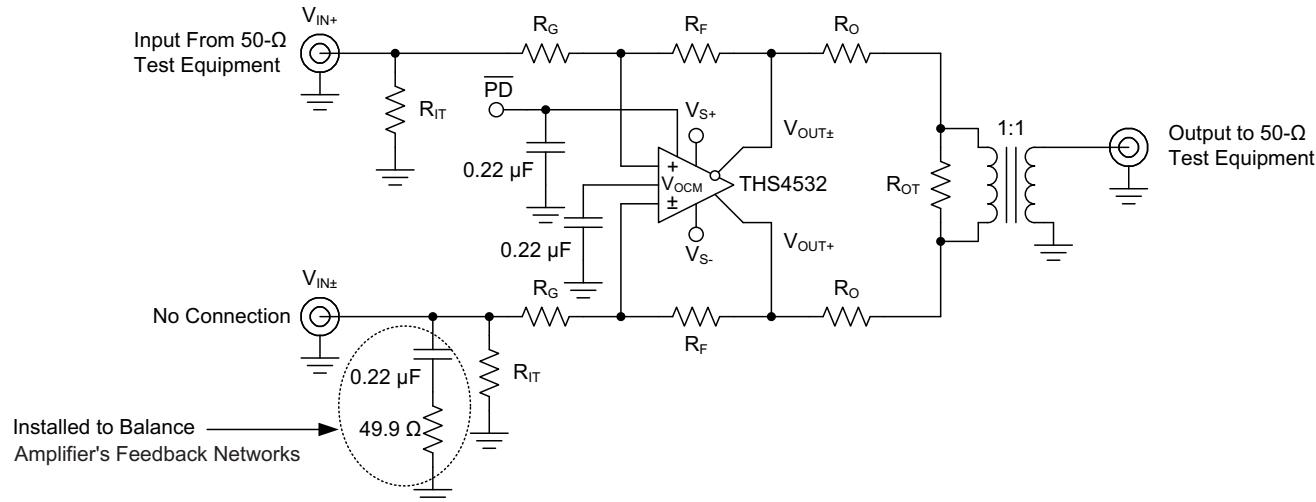

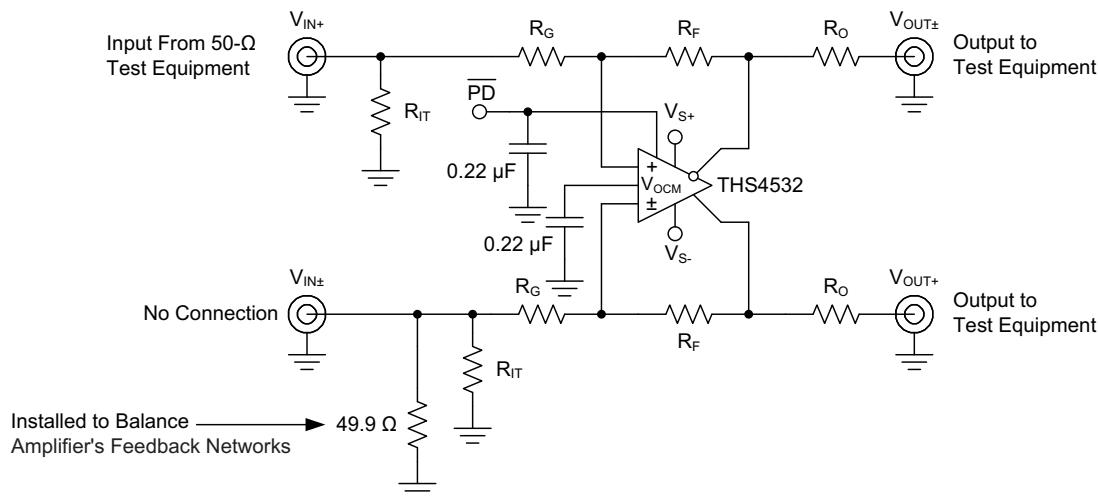

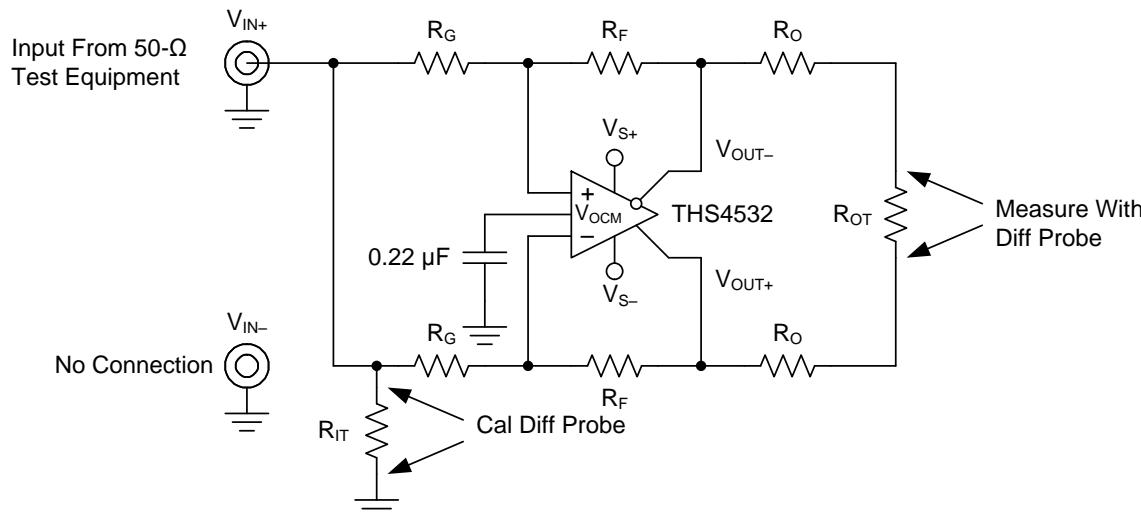

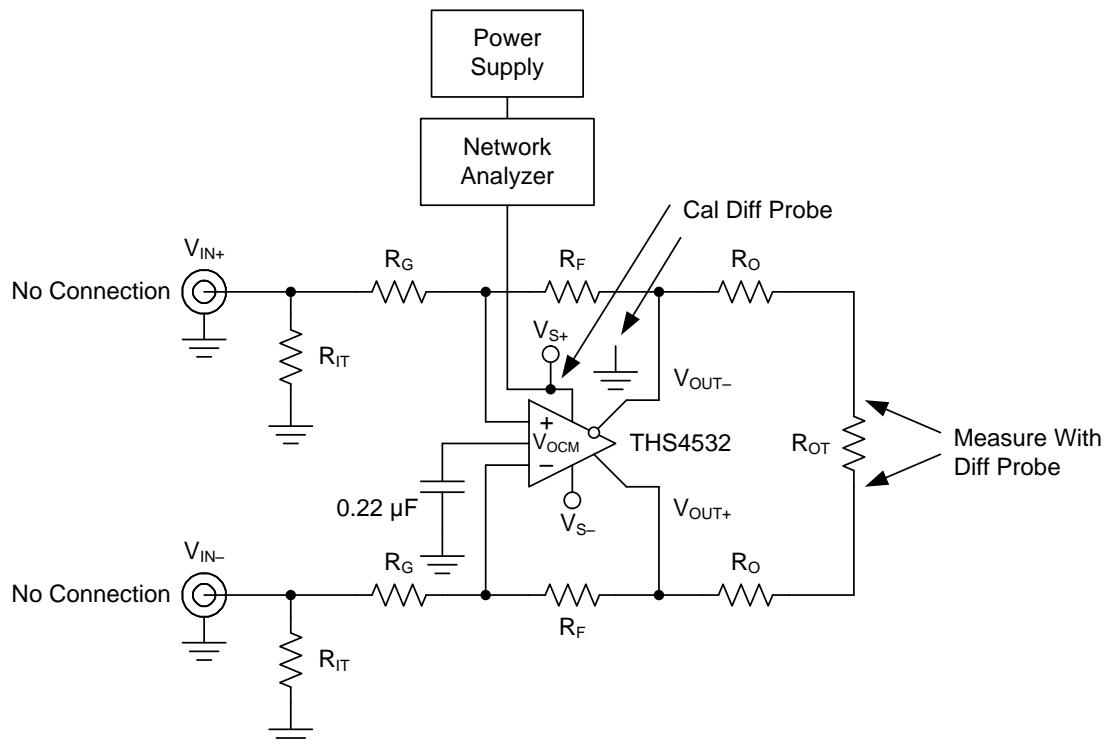

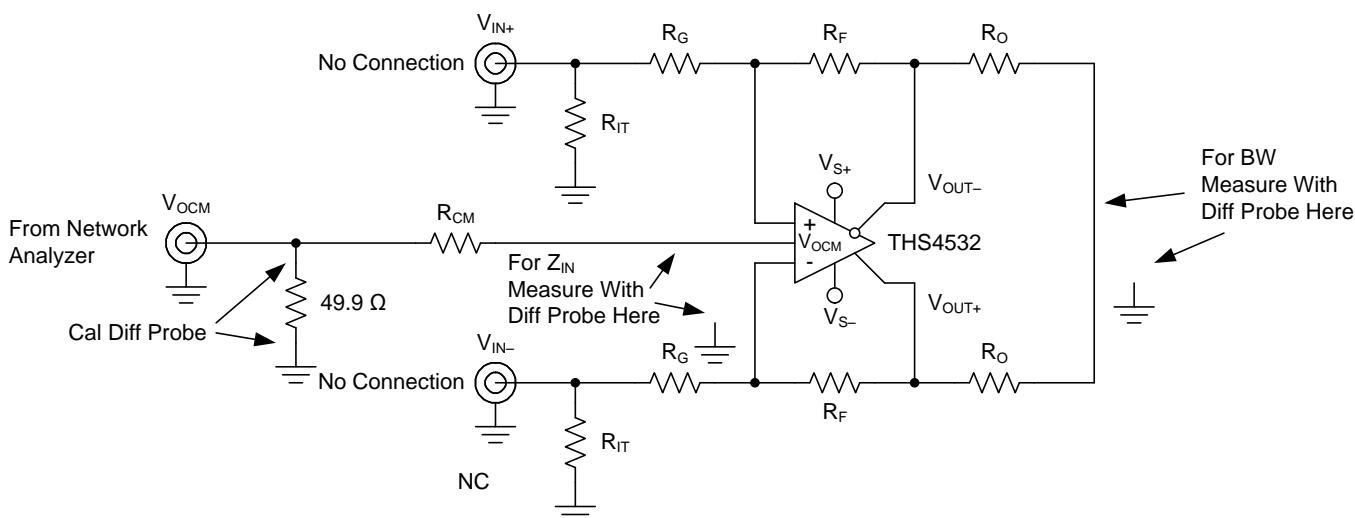

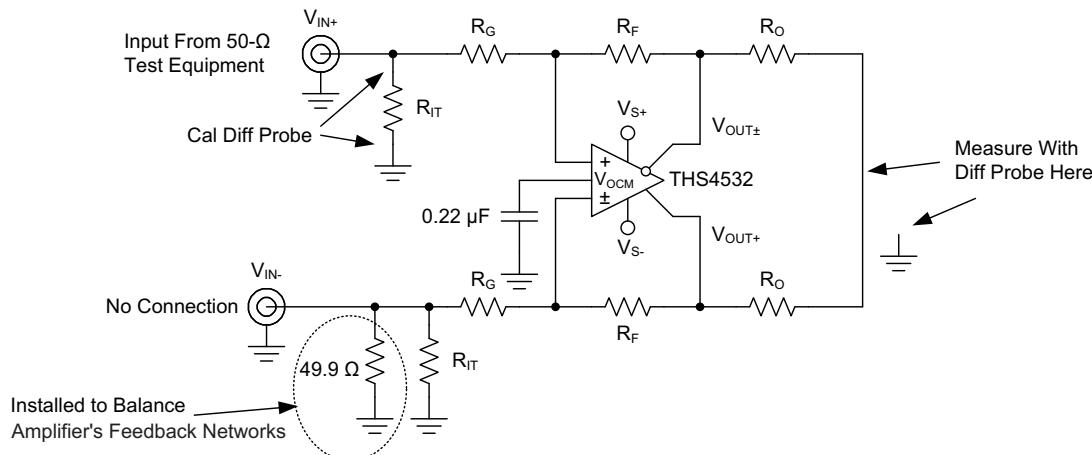

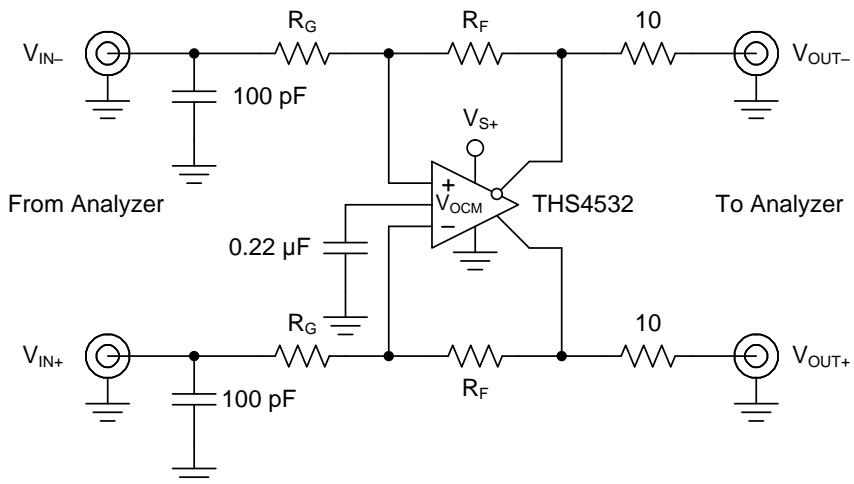

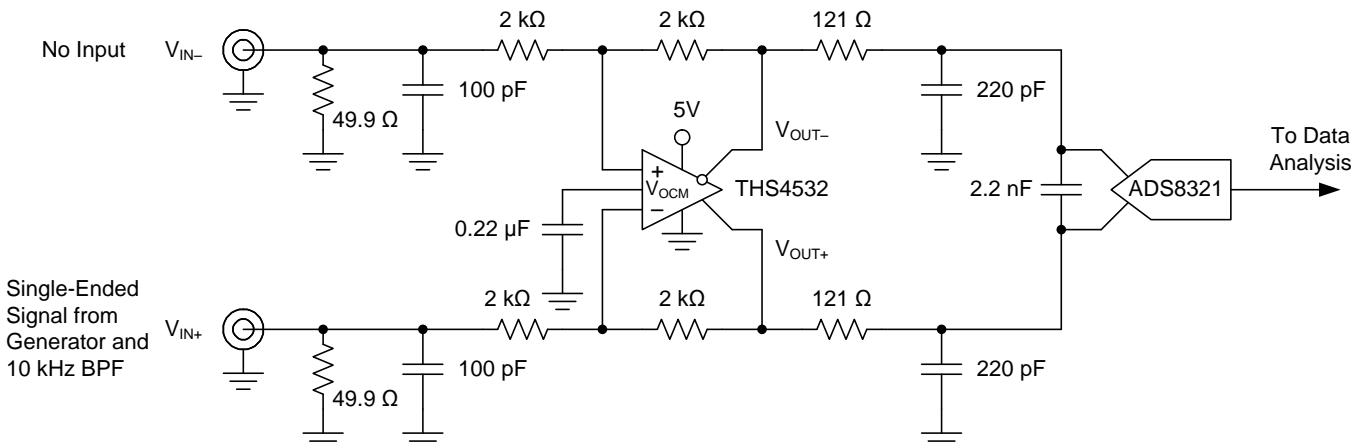

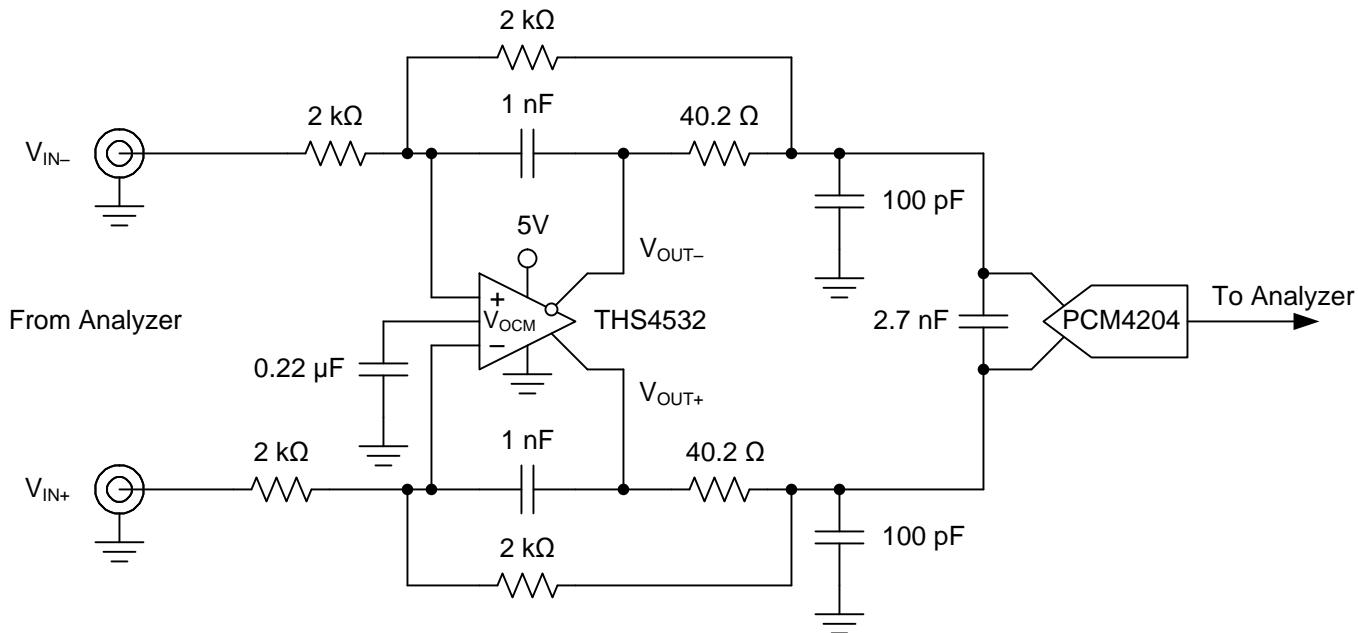

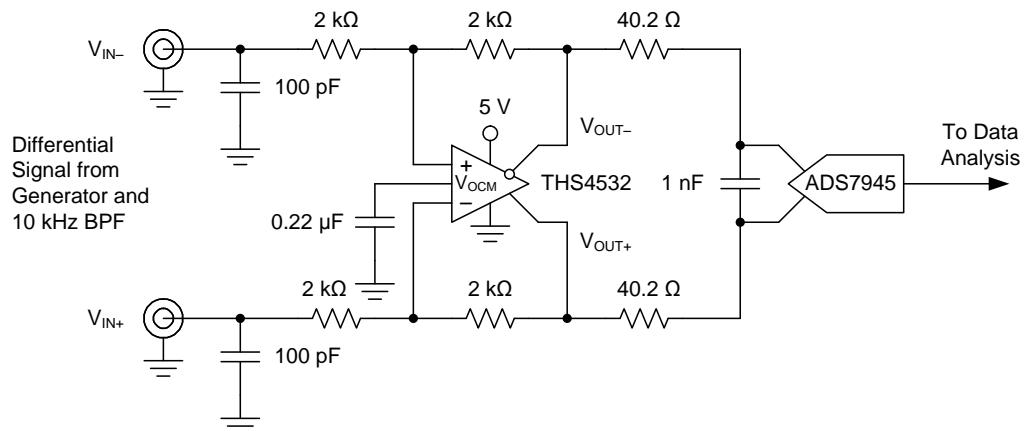

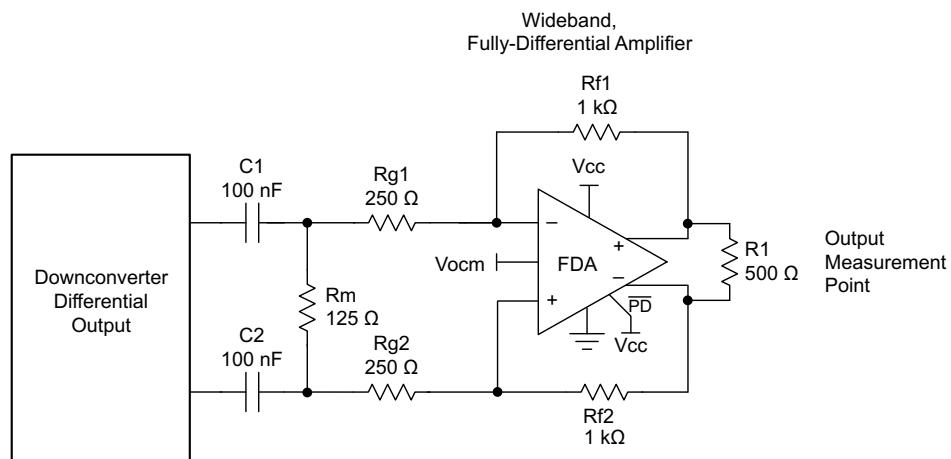

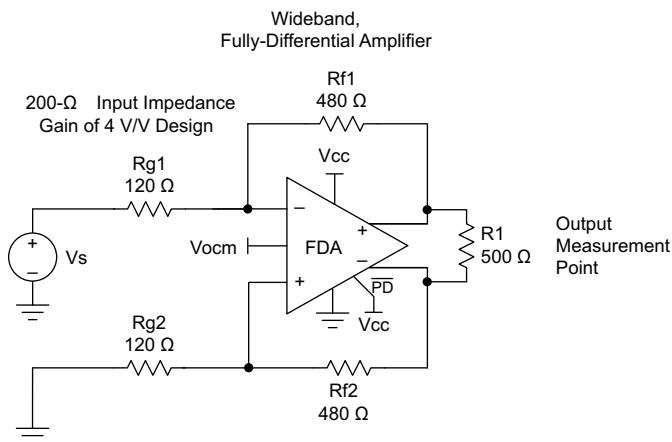

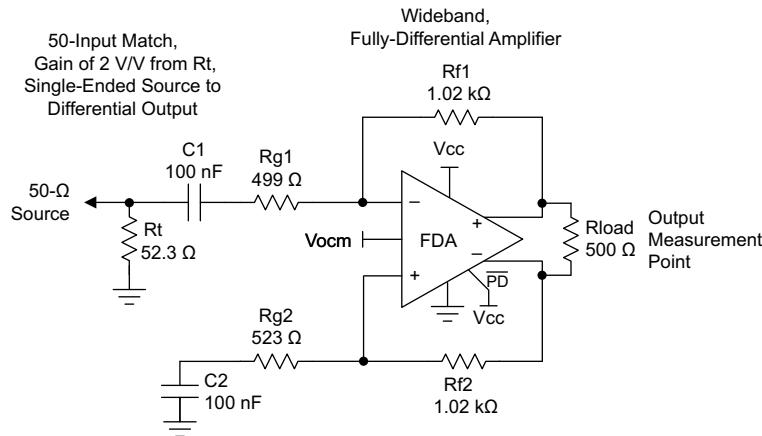

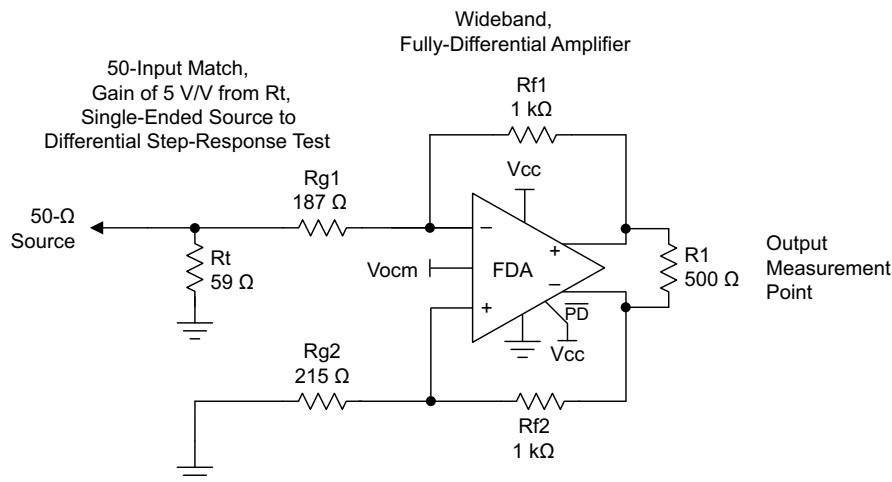

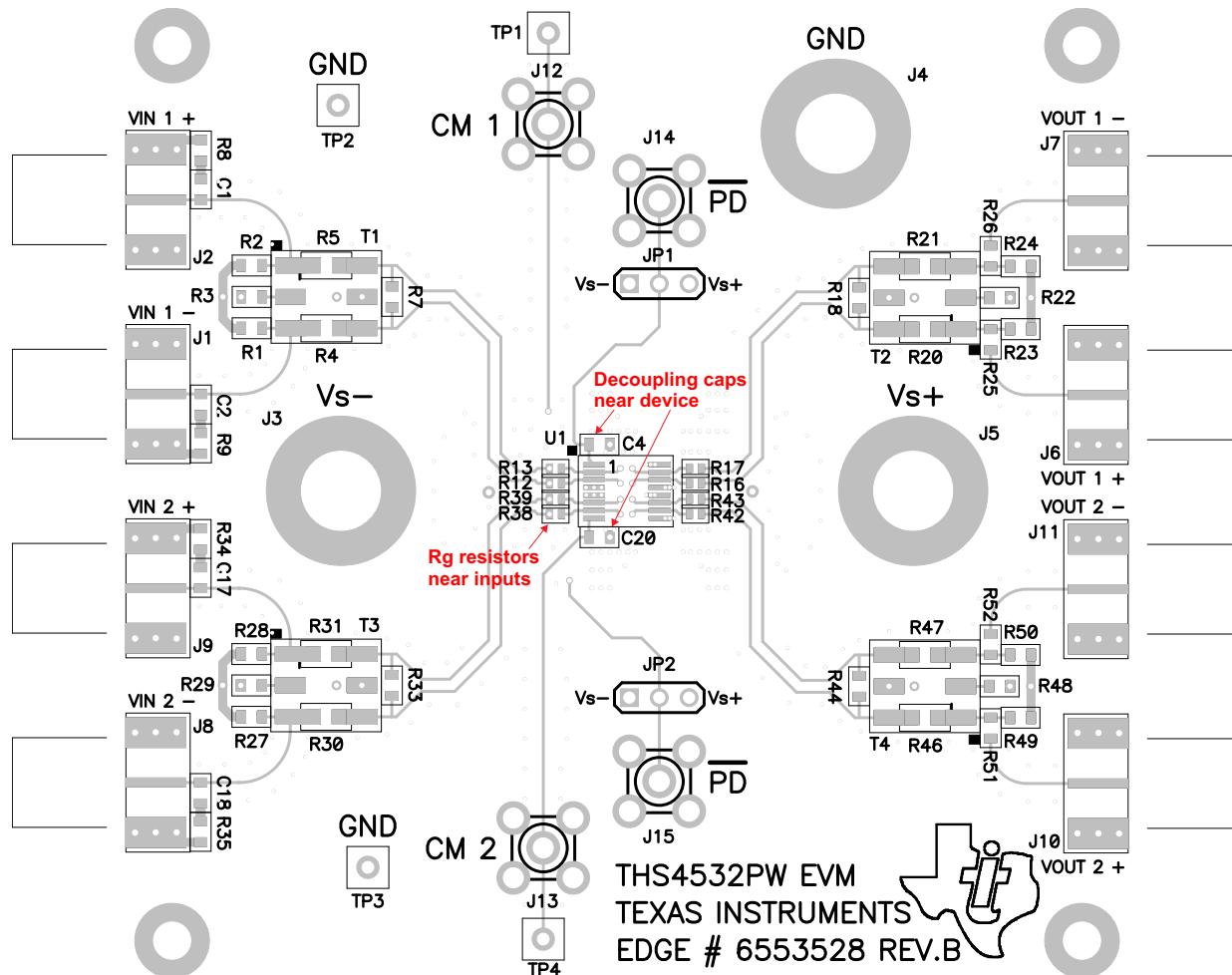

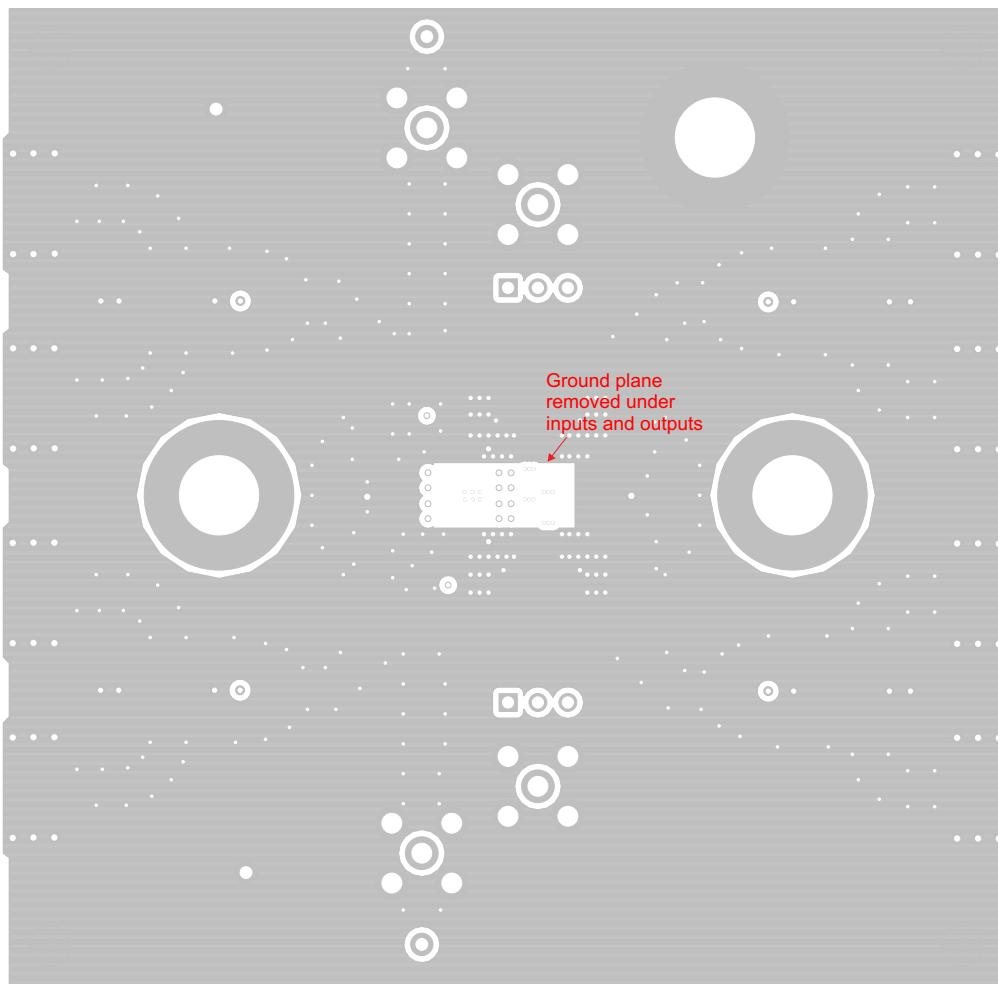

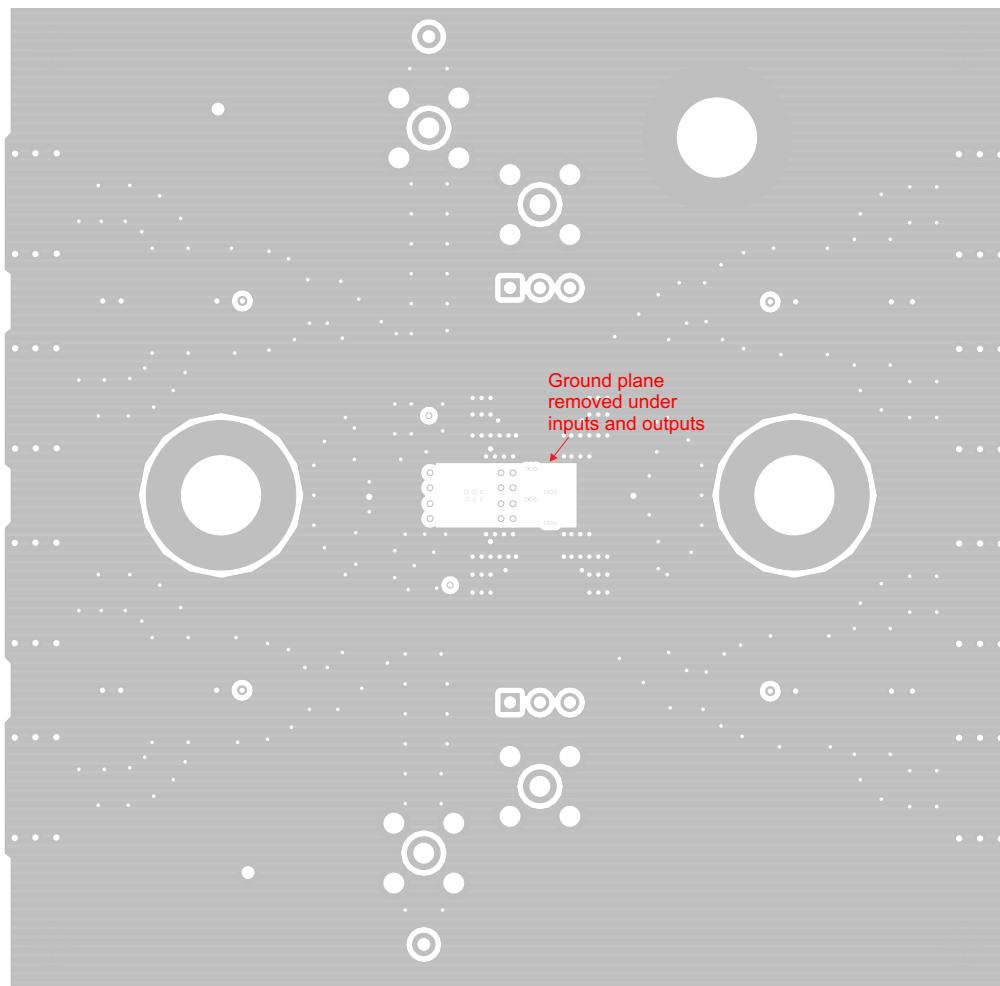

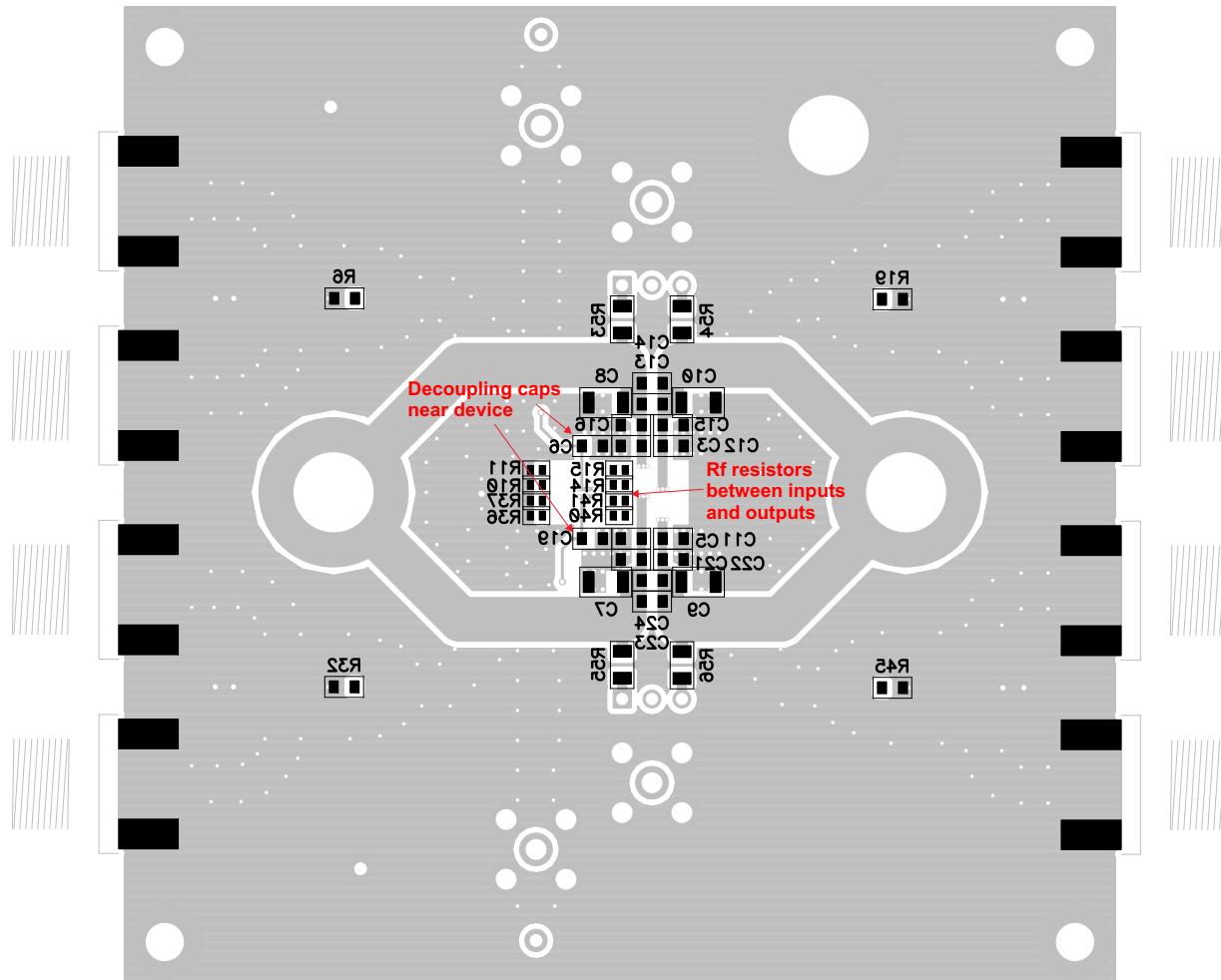

图 72 显示了在 EVM 上构建的一般测试电路，用于测试 THS4532。为了简单起见，电源供应去耦未显示 - 参见 [Layout](#) 以获得推荐。根据测试条件，组件值根据 [表 4](#) 和 [表 5](#) 进行更改，或根据需要。某些信号源使用 AC-耦合 50-Ω 源和 0.22-μF 电容以及 49.9-Ω 电阻器到地插入  $R_{IT}$  上。在未驱动或交替输入上插入一个平衡输入以平衡电路。使用分裂电源供电以简化与通用实验室测试设备的接口，但如果正确偏置，放大器可以单电源操作，如在应用部分所述，对性能没有影响。对于大多数测试，设备使用单端输入和输出变压器将差分输出转换为单端，因为通用实验室测试设备具有单端输入和输出。性能与单端输入和差分输出相同或更好。

图 72. General Test Circuit

**表 4. Gain Component Values for Single-Ended Input<sup>(1)</sup>**

| GAIN   | $R_F$ | $R_G$ | $R_{IT}$ |

|--------|-------|-------|----------|

| 1 V/V  | 2 kΩ  | 2 kΩ  | 51.1 Ω   |

| 2 V/V  | 2 kΩ  | 1 kΩ  | 52.3 Ω   |

| 5 V/V  | 2 kΩ  | 392 Ω | 53.6 Ω   |

| 10 V/V | 2 kΩ  | 187 Ω | 57.6 Ω   |

(1) Components are chosen to achieve gain and 50-Ω input termination. Resistor values shown are closest standard values so gains are approximate.

**表 5. Load Component Values For 1:1 Differential to Single-Ended Output Transformer<sup>(1)</sup>**

| $R_L$        | $R_O$         | $R_{OT}$      | ATTEN (dB) |

|--------------|---------------|---------------|------------|

| 100 $\Omega$ | 25 $\Omega$   | open          | 6          |

| 200 $\Omega$ | 84.5 $\Omega$ | 71.5 $\Omega$ | 16.7       |

| 500 $\Omega$ | 237 $\Omega$  | 56.2 $\Omega$ | 25.6       |

| 1 k $\Omega$ | 487 $\Omega$  | 52.3 $\Omega$ | 31.8       |

| 2 k $\Omega$ | 976 $\Omega$  | 51.1 $\Omega$ | 38         |

(1) The total load includes 50- $\Omega$  termination by the test equipment. Components are chosen to achieve load and 50- $\Omega$  line termination through a 1:1 transformer. Resistor values shown are closest standard values so loads are approximate.

Because of the voltage divider on the output formed by the load component values, the output of the amplifier is attenuated. The column *ATTEN* in 表 5 shows the attenuation expected from the resistor divider. When using a transformer at the output as shown in 图 72, the signal has slightly more loss because of transformer insertion loss, and these numbers are approximate. The standard output load used for most tests is 2 k $\Omega$  with associated 38 dB of loss.

### 9.1.1 Frequency Response and Output Impedance